### 80C186EB/80C188EB AND 80L186EB/80L188EB 16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS

- **■** Full Static Operation

- True CMOS Inputs and Outputs

- Integrated Feature Set

- Low-Power Static CPU Core

- Two Independent UARTs each with an Integral Baud Rate Generator

- Two 8-Bit Multiplexed I/O Ports

- Programmable Interrupt Controller

- Three Programmable 16-Bit **Timer/Counters**

- Clock Generator

- Ten Programmable Chip Selects with **Integral Wait-State Generator**

- Memory Refresh Control Unit

- System Level Testing Support (ONCE Mode)

- Direct Addressing Capability to 1 Mbyte Memory and 64 Kbyte I/O

- Speed Versions Available (5V):

- 25 MHz (80C186EB25/80C188EB25)

- 20 MHz (80C186EB20/80C188EB20)

- 13 MHz (80C186EB13/80C188EB13)

- Available in Extended Temperature Range ( $-40^{\circ}$ C to  $+85^{\circ}$ C)

- Speed Versions Available (3V):

- 16 MHz (80L186EB16/80L188EB16)

- 13 MHz (80L186EB13/80L188EB13)

- 8 MHz (80L186EB8/80L188EB8)

- Low-Power Operating Modes:

- Idle Mode Freezes CPU Clocks but keeps Peripherals Active

- Powerdown Mode Freezes All Internal Clocks

- Supports 80C187 Numeric Coprocessor Interface (80C186EB PLCC Only)

- Available In:

- 80-Pin Quad Flat Pack (QFP)

- 84-Pin Plastic Leaded Chip Carrier (PLCC)

- 80-Pin Shrink Quad Flat Pack (SQFP)

The 80C186EB is a second generation CHMOS High-Integration microprocessor. It has features that are new to the 80C186 family and include a STATIC CPU core, an enhanced Chip Select decode unit, two independent Serial Channels, I/O ports, and the capability of Idle or Powerdown low power modes.

272433-1

\*Other brands and names are the property of their respective owners.

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

| MCS-86 | 8086 - 8088 - 80C86 - 80C88 |

|--------|-----------------------------|

|        |                             |

| Ceibo      |                                           |

|------------|-------------------------------------------|

| In-Circuit | DS-186                                    |

| Emulator   |                                           |

| Supporting | http://ceibo.com/eng/products/ds186.shtml |

| MCS-86:    |                                           |

|            |                                           |

|            |                                           |

# 80C186EB/80C188EB and 80L186EB/80L188EB 16-Bit High-Integration Embedded Processors

| CONTENTS                                                                                                                                                                                                                                                                                                     | PAGE       | <b>CONTENTS</b> PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION                                                                                                                                                                                                                                                                                                 | 4          | Recommended Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CORE ARCHITECTURE  Bus Interface Unit  Clock Generator                                                                                                                                                                                                                                                       | 4          | DC SPECIFICATIONS       24         I <sub>CC</sub> versus Frequency and Voltage       27         PDTMR Pin Delay Calculation       27                                                                                                                                                                                                                                                                                                                                                                      |

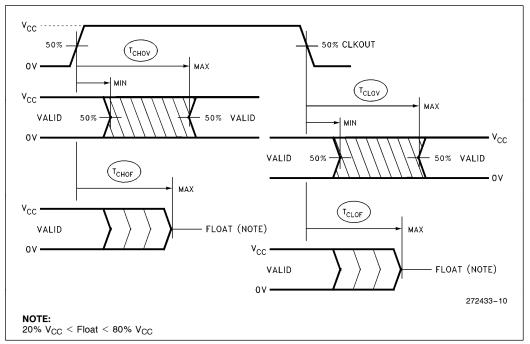

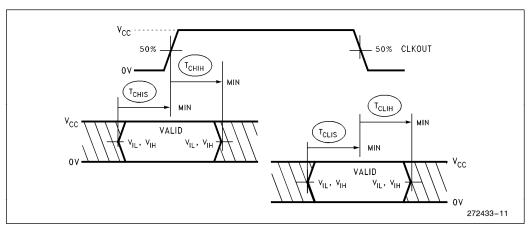

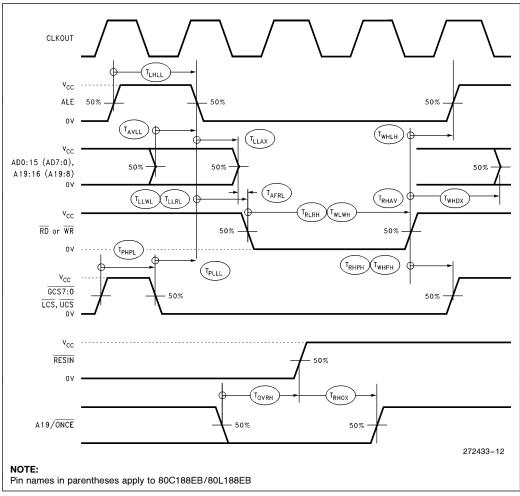

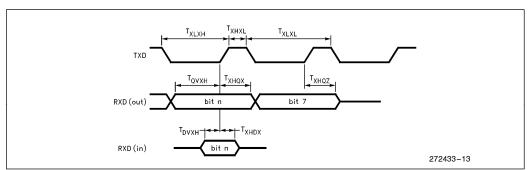

| 80C186EC PERIPHERAL ARCHITECTURE  Interrupt Control Unit Timer/Counter Unit Serial Communications Unit Chip-Select Unit I/O Port Unit Refresh Control Unit Power Management Unit 80C187 Interface (80C186EB Only) ONCE Test Mode PACKAGE INFORMATION Prefix Identification Pin Descriptions  80C186EB PINOUT | 5777777788 | AC SPECIFICATIONS       28         AC Characteristics—80C186EB25       28         AC Characteristics—80C186EB20/13       30         AC Characteristics—80L186EB16       32         Relative Timings       36         Serial Port Mode 0 Timings       37         AC TEST CONDITIONS       38         AC TIMING WAVEFORMS       38         DERATING CURVES       41         RESET       42         BUS CYCLE WAVEFORMS       45         EXECUTION TIMINGS       52         INSTRUCTION SET SUMMARY       53 |

|                                                                                                                                                                                                                                                                                                              | 14         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PACKAGE THERMAL SPECIFICATIONS                                                                                                                                                                                                                                                                               | 22         | ERRATA         59           REVISION HISTORY         59                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                    | 23         | nevision fision!59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                     | 23         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

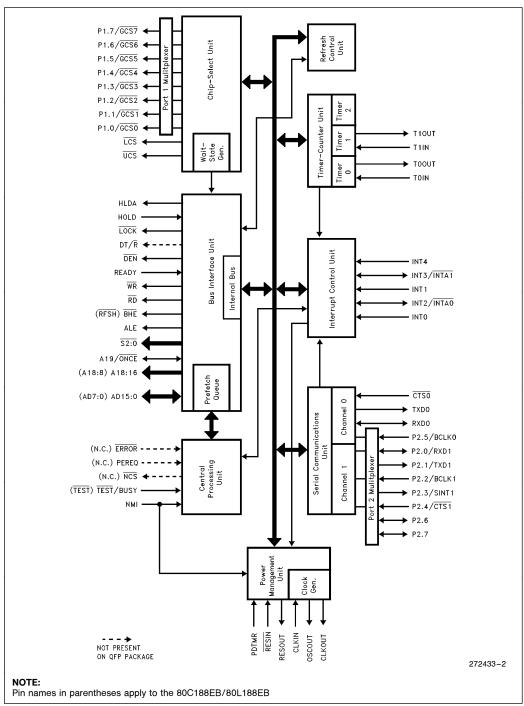

Figure 1. 80C186EB/80C188EB Block Diagram

#### INTRODUCTION

Unless specifically noted, all references to the 80C186EB apply to the 80C188EB, 80L186EB, and 80L188EB. References to pins that differ between the 80C186EB/80L186EB and the 80C188EB/80L188EB are given in parentheses. The "L" in the part number denotes low voltage operation. Physically and functionally, the "C" and "L" devices are identical.

The 80C186EB is the first product in a new generation of low-power, high-integration microprocessors. It enhances the existing 186 family by offering new features and new operating modes. The 80C186EB is object code compatible with the 80C186XL/80C188XL microprocessors.

The 80L186EB is the 3V version of the 80C186EB. The 80L186EB is functionally identical to the 80C186EB embedded processor. Current 80C186EB users can easily upgrade their designs to use the 80L186EB and benefit from the reduced power consumption inherent in 3V operation.

The feature set of the 80C186EB meets the needs of low power, space critical applications. Low-Power applications benefit from the static design of the CPU core and the integrated peripherals as well as low voltage operation. Minimum current consumption is achieved by providing a Powerdown mode that halts operation of the device, and freezes the clock circuits. Peripheral design enhancements ensure that non-initialized peripherals consume little current.

Space critical applications benefit from the integration of commonly used system peripherals. Two serial channels are provided for services such as diagnostics, inter-processor communication, modem interface, terminal display interface, and many others. A flexible chip select unit simplifies memory and peripheral interfacing. The interrupt unit provides sources for up to 129 external interrupts and will prioritize these interrupts with those generated from the on-chip peripherals. Three general purpose timer/counters and sixteen multiplexed I/O port pins round out the feature set of the 80C186EB.

Figure 1 shows a block diagram of the 80C186EB/80C188EB. The Execution Unit (EU) is an enhanced 8086 CPU core that includes: dedicated hardware to speed up effective address calculations, enhance execution speed for multiple-bit shift and rotate instructions and for multiply and divide instructions, string move instructions that operate at full bus bandwidth, ten new instruction, and fully static operation. The Bus Interface Unit (BIU) is the same as that found on the original 186 family products, ex-

cept the queue status mode has been deleted and buffer interface control has been changed to ease system design timings. An independent internal bus is used to allow communication between the BIU and internal peripherals.

#### CORE ARCHITECTURE

#### **Bus Interface Unit**

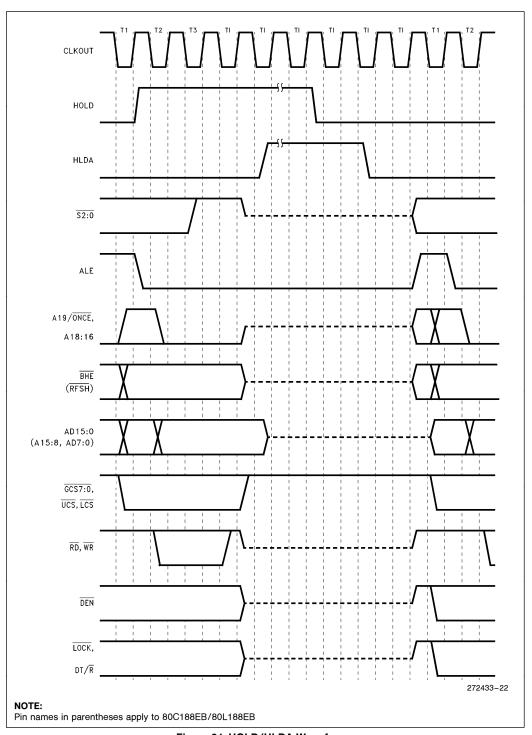

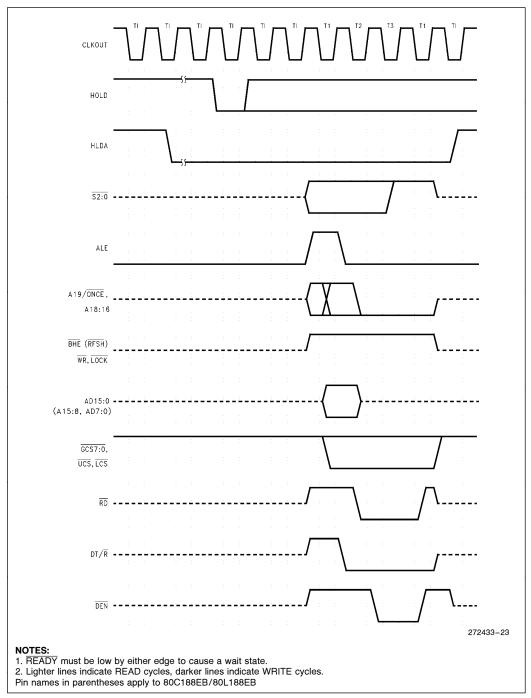

The 80C186EB core incorporates a bus controller that generates local bus control signals. In addition, it employs a HOLD/HLDA protocol to share the local bus with other bus masters.

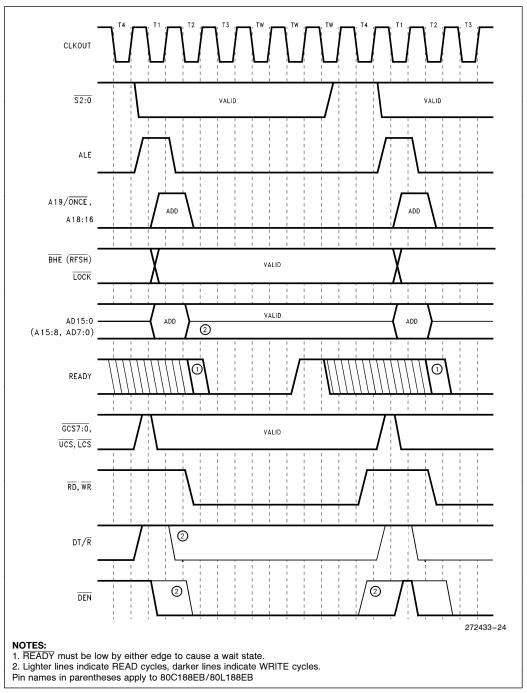

The bus controller is responsible for generating 20 bits of address, read and write strobes, bus cycle status information, and data (for write operations) information. It is also responsible for reading data off the local bus during a read operation. A READY input pin is provided to extend a bus cycle beyond the minimum four states (clocks).

The local bus controller also generates two control signals ( $\overline{\text{DEN}}$  and  $\overline{\text{DT/R}}$ ) when interfacing to external transceiver chips. (Both  $\overline{\text{DEN}}$  and  $\overline{\text{DT/R}}$  are available on the PLCC devices, only  $\overline{\text{DEN}}$  is available on the QFP and SQFP devices.) This capability allows the addition of transceivers for simple buffering of the multiplexed address/data bus.

#### **Clock Generator**

The processor provides an on-chip clock generator for both internal and external clock generation. The clock generator features a crystal oscillator, a divide-by-two counter, and two low-power operating modes

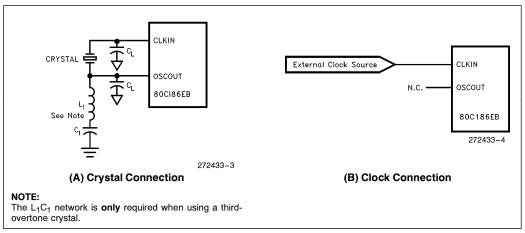

The oscillator circuit is designed to be used with either a **parallel resonant** fundamental or third-overtone mode crystal network. Alternatively, the oscillator circuit may be driven from an external clock source. Figure 2 shows the various operating modes of the oscillator circuit.

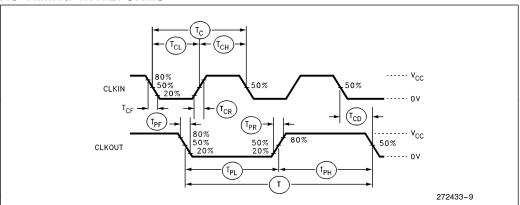

The crystal or clock frequency chosen must be twice the required processor operating frequency due to the internal divide-by-two counter. This counter is used to drive all internal phase clocks and the external CLKOUT signal. CLKOUT is a 50% duty cycle processor clock and can be used to drive other system components. All AC timings are referenced to CLKOUT.

Figure 2. Clock Configurations

The following parameters are recommended when choosing a crystal:

Temperature Range: Application Specific ESR (Equivalent Series Resistance):  $40\Omega$  max C0 (Shunt Capacitance of Crystal): 7.0 pF max C<sub>L</sub> (Load Capacitance): 20 pF  $\pm$  2 pF Drive Level: 1 mW max

80C186EB PERIPHERAL ARCHITECTURE

The 80C186EB has integrated several common system peripherals with a CPU core to create a compact, yet powerful system. The integrated peripherals are designed to be flexible and provide logical interconnections between supporting units (e.g., the interrupt control unit supports interrupt requests from the timer/counters or serial channels).

The list of integrated peripherals includes:

- 7-Input Interrupt Control Unit

- 3-Channel Timer/Counter Unit

- 2-Channel Serial Communications Unit

- 10-Output Chip-Select Unit

- I/O Port Unit

- Refresh Control Unit

- Power Management Unit

The registers associated with each integrated periheral are contained within a 128 x 16 register file called the Peripheral Control Block (PCB). The PCB can be located in either memory or I/O space on any 256 Byte address boundary.

Figure 3 provides a list of the registers associated with the PCB. The Register Bit Summary at the end of this specification individually lists all of the registers and identifies each of their programming attributes.

#### **Interrupt Control Unit**

The 80C186EB can receive interrupts from a number of sources, both internal and external. The interrupt control unit serves to merge these requests on a priority basis, for individual service by the CPU. Each interrupt source can be independently masked by the Interrupt Control Unit (ICU) or all interrupts can be globally masked by the CPU.

Internal interrupt sources include the Timers and Serial channel 0. External interrupt sources come from the five input pins INT4:0. The NMI interrupt pin is not controlled by the ICU and is passed directly to the CPU. Although the Timer and Serial channel each have only one request input to the ICU, separate vector types are generated to service individual interrupts within the Timer and Serial channel units.

#### **Timer/Counter Unit**

The 80C186EB Timer/Counter Unit (TCU) provides three 16-bit programmable timers. Two of these are highly flexible and are connected to external pins for control or clocking. A third timer is not connected to any external pins and can only be clocked internally. However, it can be used to clock the other two timer channels. The TCU can be used to count external events, time external events, generate non-repetitive waveforms, generate timed interrupts. etc.

| PCB<br>Offset | Function          |  |  |  |  |

|---------------|-------------------|--|--|--|--|

| 00H           | Reserved          |  |  |  |  |

| 02H           | End Of Interrupt  |  |  |  |  |

| 04H           | Poll              |  |  |  |  |

| 06H           | Poll Status       |  |  |  |  |

| 08H           | Interrupt Mask    |  |  |  |  |

| 0AH           | Priority Mask     |  |  |  |  |

| 0CH           | In-Service        |  |  |  |  |

| 0EH           | Interrupt Request |  |  |  |  |

| 10H           | Interrupt Status  |  |  |  |  |

| 12H           | Timer Control     |  |  |  |  |

| 14H           | Serial Control    |  |  |  |  |

| 16H           | INT4 Control      |  |  |  |  |

| 18H           | INT0 Control      |  |  |  |  |

| 1AH           | INT1 Control      |  |  |  |  |

| 1CH           | INT2 Control      |  |  |  |  |

| 1EH           | INT3 Control      |  |  |  |  |

| 20H           | Reserved          |  |  |  |  |

| 22H           | Reserved          |  |  |  |  |

| 24H           | Reserved          |  |  |  |  |

| 26H           | Reserved          |  |  |  |  |

| 28H           | Reserved          |  |  |  |  |

| 2AH           | Reserved          |  |  |  |  |

| 2CH           | Reserved          |  |  |  |  |

| 2EH           | Reserved          |  |  |  |  |

| 30H           | Timer0 Count      |  |  |  |  |

| 32H           | Timer0 Compare A  |  |  |  |  |

| 34H           | Timer0 Compare B  |  |  |  |  |

| 36H           | Timer0 Control    |  |  |  |  |

| 38H           | Timer1 Count      |  |  |  |  |

| ЗАН           | Timer1 Compare A  |  |  |  |  |

| зСН           | Timer1 Compare B  |  |  |  |  |

| 3EH           | Timer1 Control    |  |  |  |  |

| PCB<br>Offset | Function          | PCB<br>Offse | Function         | PCB<br>Offset | Function      |

|---------------|-------------------|--------------|------------------|---------------|---------------|

| 00H           | Reserved          | 40H          | Timer2 Count     | H08           | GCS0 Start    |

| 02H           | End Of Interrupt  | 42H          | Timer2 Compare   | 82H           | GCS0 Stop     |

| 04H           | Poll              | 44H          | Reserved         | 84H           | GCS1 Start    |

| 06H           | Poll Status       | 46H          | Timer2 Control   | 86H           | GCS1 Stop     |

| H80           | Interrupt Mask    | 48H          | Reserved         | H88           | GCS2 Start    |

| 0AH           | Priority Mask     | 4AH          | Reserved         | HA8           | GCS2 Stop     |

| 0CH           | In-Service        | 4CH          | Reserved         | 8CH           | GCS3 Start    |

| 0EH           | Interrupt Request | 4EH          | Reserved         | 8EH           | GCS3 Stop     |

| 10H           | Interrupt Status  | 50H          | Port 1 Direction | 90H           | GCS4 Start    |

| 12H           | Timer Control     | 52H          | Port 1 Pin       | 92H           | GCS4 Stop     |

| 14H           | Serial Control    | 54H          | Port 1 Control   | 94H           | GCS5 Start    |

| 16H           | INT4 Control      | 56H          | Port 1 Latch     | 96H           | GCS5 Stop     |

| 18H           | INT0 Control      | 58H          | Port 2 Direction | 98H           | GCS6 Start    |

| 1AH           | INT1 Control      | 5AH          | Port 2 Pin       | 9AH           | GCS6 Stop     |

| 1CH           | INT2 Control      | 5CH          | Port 2 Control   | 9CH           | GCS7 Start    |

| 1EH           | INT3 Control      | 5EH          | Port 2 Latch     | 9EH           | GCS7 Stop     |

| 20H           | Reserved          | 60H          | Serial0 Baud     | A0H           | LCS Start     |

| 22H           | Reserved          | 62H          | Serial0 Count    | A2H           | LCS Stop      |

| 24H           | Reserved          | 64H          | Serial0 Control  | A4H           | UCS Start     |

| 26H           | Reserved          | 66H          | Serial0 Status   | A6H           | UCS Stop      |

| 28H           | Reserved          | 68H          | Serial0 RBUF     | A8H           | Relocation    |

| 2AH           | Reserved          | 6AH          | Serial0 TBUF     | AAH           | Reserved      |

| 2CH           | Reserved          | 6CH          | Reserved         | ACH           | Reserved      |

| 2EH           | Reserved          | 6EH          | Reserved         | AEH           | Reserved      |

| 30H           | Timer0 Count      | 70H          | Serial1 Baud     | В0Н           | Refresh Base  |

| 32H           | Timer0 Compare A  | 72H          | Serial1 Count    | B2H           | Refresh Time  |

| 34H           | Timer0 Compare B  | 74H          | Serial1 Control  | В4Н           | Refresh Contr |

| 36H           | Timer0 Control    | 76H          | Serial1 Status   | В6Н           | Reserved      |

| 38H           | Timer1 Count      | 78H          | Serial1 RBUF     | В8Н           | Power Contro  |

| ЗАН           | Timer1 Compare A  | 7AH          | Serial1 TBUF     | BAH           | Reserved      |

| 3СН           | Timer1 Compare B  | 7CH          | Reserved         | всн           | Step ID       |

| 3EH           | Timer1 Control    | 7EH          | Reserved         | BEH           | Reserved      |

| PCB<br>Offset | Function        |

|---------------|-----------------|

| 80H           | GCS0 Start      |

| 82H           | GCS0 Stop       |

| 84H           | GCS1 Start      |

| 86H           | GCS1 Stop       |

| 88H           | GCS2 Start      |

| 8AH           | GCS2 Stop       |

| 8CH           | GCS3 Start      |

| 8EH           | GCS3 Stop       |

| 90H           | GCS4 Start      |

| 92H           | GCS4 Stop       |

| 94H           | GCS5 Start      |

| 96H           | GCS5 Stop       |

| 98H           | GCS6 Start      |

| 9AH           | GCS6 Stop       |

| 9CH           | GCS7 Start      |

| 9EH           | GCS7 Stop       |

| A0H           | LCS Start       |

| A2H           | LCS Stop        |

| A4H           | UCS Start       |

| A6H           | UCS Stop        |

| A8H           | Relocation      |

| AAH           | Reserved        |

| ACH           | Reserved        |

| AEH           | Reserved        |

| вон           | Refresh Base    |

| B2H           | Refresh Time    |

| В4Н           | Refresh Control |

| В6Н           | Reserved        |

| В8Н           | Power Control   |

| BAH           | Reserved        |

| всн           | Step ID         |

| BEH           | Reserved        |

| PCB<br>Offset | Function |

|---------------|----------|

| C0H           | Reserved |

| C2H           | Reserved |

| C4H           | Reserved |

| С6Н           | Reserved |

| C8H           | Reserved |

| CAH           | Reserved |

| CCH           | Reserved |

| CEH           | Reserved |

| D0H           | Reserved |

| D2H           | Reserved |

| D4H           | Reserved |

| D6H           | Reserved |

| D8H           | Reserved |

| DAH           | Reserved |

| DCH           | Reserved |

| DEH           | Reserved |

| E0H           | Reserved |

| E2H           | Reserved |

| E4H           | Reserved |

| E6H           | Reserved |

| E8H           | Reserved |

| EAH           | Reserved |

| ECH           | Reserved |

| EEH           | Reserved |

| F0H           | Reserved |

| F2H           | Reserved |

| F4H           | Reserved |

| F6H           | Reserved |

| F8H           | Reserved |

| FAH           | Reserved |

| FCH           | Reserved |

|               |          |

Figure 3. Peripheral Control Block Registers

FEH

Reserved

#### **Serial Communications Unit**

The Serial Control Unit (SCU) of the 80C186EB contains two independent channels. Each channel is identical in operation except that only channel 0 is supported by the integrated interrupt controller (channel 1 has an external interrupt pin). Each channel has its own baud rate generator that is independent of the Timer/Counter Unit, and can be internally or externally clocked at up to one half the 80C186EB operating frequency.

Independent baud rate generators are provided for each of the serial channels. For the asynchronous modes, the generator supplies an 8x baud clock to both the receive and transmit register logic. A 1x baud clock is provided in the synchronous mode.

#### **Chip-Select Unit**

The 80C186EB Chip-Select Unit (CSU) integrates logic which provides up to ten programmable chipselects to access both memories and peripherals. In addition, each chip-select can be programmed to automatically insert additional clocks (wait-states) into the current bus cycle and automatically terminate a bus cycle independent of the condition of the READY input pin.

#### I/O Port Unit

The I/O Port Unit (IPU) on the 80C186EB supports two 8-bit channels of input, output, or input/output operation. Port 1 is multiplexed with the chip select pins and is output only. Most of Port 2 is multiplexed with the serial channel pins. Port 2 pins are limited to either an output or input function depending on the operation of the serial pin it is multiplexed with.

#### **Refresh Control Unit**

The Refresh Control Unit (RCU) automatically generates a periodic memory read bus cycle to keep dynamic or pseudo-static memory refreshed. A 9-bit counter controls the number of clocks between refresh requests.

#### 80C186EB/80C188EB, 80L186EB/80L188EB

A 12-bit address generator is maintained by the RCU and is presented on the A12:1 address lines during the refresh bus cycle. Address bits A19:13 are programmable to allow the refresh address block to be located on any 8 Kbyte boundary.

#### **Power Management Unit**

The 80C186EB Power Management Unit (PMU) is provided to control the power consumption of the device. The PMU provides three power modes: Active, Idle, and Powerdown.

Active Mode indicates that all units on the 80C186EB are functional and the device consumes maximum power (depending on the level of peripheral operation). Idle Mode freezes the clocks of the Execution and Bus units at a logic zero state (all peripherals continue to operate normally).

The Powerdown mode freezes all internal clocks at a logic zero level and disables the crystal oscillator. All internal registers hold their values provided  $V_{\rm CC}$  is maintained. Current consumption is reduced to just transistor junction leakage.

#### 80C187 Interface (80C186EB Only)

The 80C186EB (PLCC package only) supports the direct connection of the 80C187 Numerics Coprocessor.

#### **ONCE Test Mode**

To facilitate testing and inspection of devices when fixed into a target system, the 80C186EB has a test mode available which forces all output and input/output pins to be placed in the high-impedance state. ONCE stands for "ON Circuit Emulation". The ONCE mode is selected by forcing the A19/ONCE pin LOW (0) during a processor reset (this pin is weakly held to a HIGH (1) level) while RESIN is active

#### PACKAGE INFORMATION

This section describes the pins, pinouts, and thermal characteristics for the 80C186EB in the Plastic Leaded Chip Carrier (PLCC) package, Shrink Quad Flat Pack (SQFP), and Quad Flat Pack (QFP) package. For complete package specifications and information, see the Intel Packaging Outlines and Dimensions Guide (Order Number: 231369).

#### **Prefix Identification**

With the extended temperature range, operational characteristics are guaranteed over the temperature range corresponding to  $-40^{\circ}$ C to  $+85^{\circ}$ C ambient. Package types are identified by a two-letter prefix to the part number. The prefixes are listed in Table 1.

Table 1. Prefix Identification

| Prefix | Note | Package<br>Type | Temperature<br>Type |

|--------|------|-----------------|---------------------|

| TN     |      | PLCC            | Extended            |

| TS     |      | QFP (EIAJ)      | Extended            |

| SB     | 1    | SQFP            | Extended/Commercial |

| N      | 1    | PLCC            | Commercial          |

| S      | 1    | QFP (EIAJ)      | Commercial          |

#### NOTE:

1. The 5V 25 MHz and 3V 16 MHz versions are only available in commercial temperature range corresponding to  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  ambient.

#### **Pin Descriptions**

Each pin or logical set of pins is described in Table 3. There are three columns for each entry in the Pin Description Table.

The **Pin Name** column contains a mnemonic that describes the pin function. Negation of the signal name (for example, RESIN) denotes a signal that is active low.

The **Pin Type** column contains two kinds of information. The first symbol indicates whether a pin is power (P), ground (G), input only (I), output only (O) or input/output (I/O). Some pins have multiplexed functions (for example, A19/S6). Additional symbols indicate additional characteristics for each pin. Table 2 lists all the possible symbols for this column.

The **Input Type** column indicates the type of input (Asynchronous or Synchronous).

Asynchronous pins require that setup and hold times be met only in order to guarantee *recognition* at a particular clock edge. Synchronous pins require that setup and hold times be met to guarantee proper *operation*. For example, missing the setup or hold time for the SRDY pin (a synchronous input) will result in a system failure or lockup. Input pins may also be edge- or level-sensitive. The possible characteristics for input pins are S(E), S(L), A(E) and A(L).

The **Output States** column indicates the output state as a function of the device operating mode. Output states are dependent upon the current activity of the processor. There are four operational states that are different from regular operation: bus hold, reset, Idle Mode and Powerdown Mode. Appropriate characteristics for these states are also indicated in this column, with the legend for all possible characteristics in Table 2.

The **Pin Description** column contains a text description of each pin.

As an example, consider AD15:0. I/O signifies the pins are bidirectional. S(L) signifies that the input function is synchronous and level-sensitive. H(Z) signifies that, as outputs, the pins are high-impedance upon acknowledgement of bus hold. R(Z) signifies that the pins float during reset. P(X) signifies that the pins retain their states during Powerdown Mode.

**Table 2. Pin Description Nomenclature**

| rable 2. Pin Description Nomenciature |                                                        |  |  |  |  |  |

|---------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| Symbol                                | Description                                            |  |  |  |  |  |

| Р                                     | Power Pin (Apply + V <sub>CC</sub> Voltage)            |  |  |  |  |  |

| G                                     | Ground (Connect to V <sub>SS</sub> )                   |  |  |  |  |  |

| I                                     | Input Only Pin                                         |  |  |  |  |  |

| 0                                     | Output Only Pin                                        |  |  |  |  |  |

| 1/0                                   | Input/Output Pin                                       |  |  |  |  |  |

| S(E)                                  | Synchronous, Edge Sensitive                            |  |  |  |  |  |

| S(L)                                  | Synchronous, Level Sensitive                           |  |  |  |  |  |

| A(E)                                  | Asynchronous, Edge Sensitive                           |  |  |  |  |  |

| A(L)                                  | Asynchronous, Level Sensitive                          |  |  |  |  |  |

| H(1)                                  | Output Driven to V <sub>CC</sub> during Bus Hold       |  |  |  |  |  |

| H(0)                                  | Output Driven to V <sub>SS</sub> during Bus Hold       |  |  |  |  |  |

| H(Z)                                  | Output Floats during Bus Hold                          |  |  |  |  |  |

| H(Q)                                  | Output Remains Active during Bus Hold                  |  |  |  |  |  |

| H(X)                                  | Output Retains Current State during Bus Hold           |  |  |  |  |  |

| R(WH)                                 | Output Weakly Held at V <sub>CC</sub> during Reset     |  |  |  |  |  |

| R(1)                                  | Output Driven to V <sub>CC</sub> during Reset          |  |  |  |  |  |

| R(0)                                  | Output Driven to V <sub>SS</sub> during Reset          |  |  |  |  |  |

| R(Z)                                  | Output Floats during Reset                             |  |  |  |  |  |

| R(Q)                                  | Output Remains Active during Reset                     |  |  |  |  |  |

| R(X)                                  | Output Retains Current State during Reset              |  |  |  |  |  |

| l(1)                                  | Output Driven to V <sub>CC</sub> during Idle Mode      |  |  |  |  |  |

| I(0)                                  | Output Driven to V <sub>SS</sub> during Idle Mode      |  |  |  |  |  |

| I(Z)                                  | Output Floats during Idle Mode                         |  |  |  |  |  |

| I(Q)                                  | Output Remains Active during Idle Mode                 |  |  |  |  |  |

| I(X)                                  | Output Retains Current State during Idle Mode          |  |  |  |  |  |

| P(1)                                  | Output Driven to V <sub>CC</sub> during Powerdown Mode |  |  |  |  |  |

| P(0)                                  | Output Driven to V <sub>SS</sub> during Powerdown Mode |  |  |  |  |  |

| P(Z)                                  | Output Floats during Powerdown Mode                    |  |  |  |  |  |

| P(Q)                                  | Output Remains Active during Powerdown Mode            |  |  |  |  |  |

| P(X)                                  | Output Retains Current State during Powerdown Mode     |  |  |  |  |  |

**Table 3. Pin Descriptions**

| Pin Din Input Output |             |               |                       |                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------------------|-------------|---------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin<br>Name          | Pin<br>Type | Input<br>Type | Output<br>States      | Description                                                                                                                                                                                                                                                                                                                                         |  |  |

| V <sub>CC</sub>      | Р           | _             | _                     | <b>POWER</b> connections consist of four pins which must be shorted externally to a V <sub>CC</sub> board plane.                                                                                                                                                                                                                                    |  |  |

| V <sub>SS</sub>      | G           | _             | _                     | <b>GROUND</b> connections consist of six pins which must be shorted externally to a V <sub>SS</sub> board plane.                                                                                                                                                                                                                                    |  |  |

| CLKIN                | I           | A(E)          | _                     | CLock INput is an input for an external clock. An external oscillator operating at two times the required processor operating frequency can be connected to CLKIN. For crystal operation, CLKIN (along with OSCOUT) are the crystal connections to an internal Pierce oscillator.                                                                   |  |  |

| OSCOUT               | 0           | 1             | H(Q)<br>R(Q)<br>P(Q)  | OSCillator OUTput is only used when using a crystal to generate the external clock. OSCOUT (along with CLKIN) are the crystal connections to an internal Pierce oscillator. This pin is not to be used as 2X clock output for non-crystal applications (i.e., this pin is N.C. for non-crystal applications). OSCOUT does not float in ONCE mode.   |  |  |

| CLKOUT               | 0           | 1             | H(Q)<br>R(Q)<br>P(Q)  | CLock OUTput provides a timing reference for inputs and outputs of the processor, and is one-half the input clock (CLKIN) frequency. CLKOUT has a 50% duty cycle and transistions every falling edge of CLKIN.                                                                                                                                      |  |  |

| RESIN                | I           | A(L)          | Ι                     | RESet IN causes the processor to immediately terminate any bus cycle in progress and assume an initialized state. All pins will be driven to a known state, and RESOUT will also be driven active. The rising edge (low-to-high) transition synchronizes CLKOUT with CLKIN before the processor begins fetching opcodes at memory location 0FFFF0H. |  |  |

| RESOUT               | 0           | 1             | H(0)<br>R(1)<br>P(0)  | RESet OUTput that indicates the processor is currently in the reset state. RESOUT will remain active as long as RESIN remains active.                                                                                                                                                                                                               |  |  |

| PDTMR                | 1/0         | A(L)          | H(WH)<br>R(Z)<br>P(1) | Power-Down TiMeR pin (normally connected to an external capacitor) that determines the amount of time the processor waits after an exit from power down before resuming normal operation. The duration of time required will depend on the startup characteristics of the crystal oscillator.                                                       |  |  |

| NMI                  | I           | A(E)          | _                     | Non-Maskable Interrupt input causes a TYPE-2 interrupt to be serviced by the CPU. NMI is latched internally.                                                                                                                                                                                                                                        |  |  |

| TEST/BUSY<br>(TEST)  | I           | A(E)          | _                     | TEST is used during the execution of the WAIT instruction to suspend CPU operation until the pin is sampled active (LOW). TEST is alternately known as BUSY when interfacing with an 80C187 numerics coprocessor (80C186EB only).                                                                                                                   |  |  |

| AD15:0<br>(AD7:0)    | 1/0         | S(L)          | H(Z)<br>R(Z)<br>P(X)  | These pins provide a multiplexed <b>Address</b> and <b>Data</b> bus. During the address phase of the bus cycle, address bits 0 through 15 (0 through 7 on the 80C188EB) are presented on the bus and can be latched using ALE. 8- or 16-bit data information is transferred during the data phase of the bus cycle.                                 |  |  |

**NOTE:** Pin names in parentheses apply to the 80C188EB/80L188EB.

Table 3. Pin Descriptions (Continued)

| Pin<br>Name                                              | Pin<br>Type | Input<br>Type | Output<br>States      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |                            |                                                                                                                                    |  |

|----------------------------------------------------------|-------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| A18:16<br>A19/ONCE<br>(A15:A8)<br>(A18:16)<br>(A19/ONCE) | I/O         | A(L)          | H(Z)<br>R(WH)<br>P(X) | These pins provide multiplexed <b>Address</b> during the address phase of the bus cycle. Address bits 16 through 19 are presented on these pins and can be latched using ALE. These pins are driven to a logic 0 during the data phase of the bus cycle. On the 80C188EB, A15–A8 provide valid address information for the entire bus cycle. During a processor reset (RESIN active), A19/ONCE is used to enable ONCE mode. A18:16 must not be driven low during reset or improper operation may result. |                            |                            |                                                                                                                                    |  |

| S2:0                                                     | 0           | _             | H(Z)<br>R(Z)          | Bus cycle <b>Status</b> are encoded on these pins to provide bus transaction information. S2:0 are encoded as follows:                                                                                                                                                                                                                                                                                                                                                                                   |                            |                            |                                                                                                                                    |  |

|                                                          |             |               | P(1)                  | <u>S2</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>S1</u>                  | <u>50</u>                  | Bus Cycle Initiated                                                                                                                |  |

|                                                          |             |               |                       | 0<br>0<br>0<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0<br>0<br>1<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | Interrupt Acknowledge Read I/O Write I/O Processor HALT Queue Instruction Fetch Read Memory Write Memory Passive (no bus activity) |  |

| ALE                                                      | 0           | _             | H(0)<br>R(0)<br>P(0)  | Address Latch Enable output is used to strobe address information into a transparent type latch during the address phase of the bus cycle.                                                                                                                                                                                                                                                                                                                                                               |                            |                            |                                                                                                                                    |  |

| BHE<br>(RFSH)                                            | 0           | _             | H(Z)<br>R(Z)<br>P(X)  | Byte High Enable output to indicate that the bus cycle in progress is transferring data over the upper half of the data bus. BHE and A0 have the following logical encoding                                                                                                                                                                                                                                                                                                                              |                            |                            |                                                                                                                                    |  |

|                                                          |             |               |                       | Α0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BI                         | ΤE                         | Encoding (for the 80C186EB/80L186EB only)                                                                                          |  |

|                                                          |             |               |                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |                            |                                                                                                                                    |  |

|                                                          |             |               |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | JS CYC                     |                                                                                                                                    |  |

| RD                                                       | 0           | _             | H(Z)<br>R(Z)<br>P(1)  | ReaD output signals that the accessed memory or I/O device must drive data information onto the data bus.                                                                                                                                                                                                                                                                                                                                                                                                |                            |                            |                                                                                                                                    |  |

| WR                                                       | 0           | _             | H(Z)<br>R(Z)<br>P(1)  | WRite output signals that data available on the data bus are to be written into the accessed memory or I/O device.                                                                                                                                                                                                                                                                                                                                                                                       |                            |                            |                                                                                                                                    |  |

| READY                                                    | I           | A(L)<br>S(L)  | _                     | <b>READY</b> input to signal the completion of a bus cycle. READY must be active to terminate any bus cycle, unless it is ignored by correctly programming the Chip-Select Unit.                                                                                                                                                                                                                                                                                                                         |                            |                            |                                                                                                                                    |  |

| DEN                                                      | 0           | _             | H(Z)<br>R(Z)<br>P(1)  | <b>Data ENable</b> output to control the <u>enable</u> of bi-directional transceivers in a buffered system. DEN is active only when data is to be transferred on the bus.                                                                                                                                                                                                                                                                                                                                |                            |                            |                                                                                                                                    |  |

**NOTE:** Pin names in parentheses apply to the 80C188EB/80L188EB.

Table 3. Pin Descriptions (Continued)

| Pin<br>Name                                                                                          | Pin<br>Type | Input<br>Type | Output<br>States               | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------|-------------|---------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DT/R                                                                                                 | 0           | _             | H(Z)<br>R(Z)<br>P(X)           | <b>Data Transmit/Receive</b> output controls the direction of a bi-directional buffer in a buffered system. DT/ $\overline{R}$ is only available for the PLCC package.                                                                                                                                                                                                                                                   |

| LOCK                                                                                                 | 0           | _             | H(Z)<br>R(WH)<br>P(1)          | LOCK output indicates that the bus cycle in progress is not to be interrupted. The processor will not service other bus requests (such as HOLD) while LOCK is active. This pin is configured as a weakly held high input while RESIN is active and must not be driven low.                                                                                                                                               |

| HOLD                                                                                                 | I           | A(L)          | _                              | <b>HOLD</b> request input to signal that an external bus master wishes to gain control of the local bus. The processor will relinquish control of the local bus between instruction boundaries not conditioned by a LOCK prefix.                                                                                                                                                                                         |

| HLDA                                                                                                 | 0           | _             | H(1)<br>R(0)<br>P(0)           | HoLD Acknowledge output to indicate that the processor has relinquished control of the local bus. When HLDA is asserted, the processor will (or has) floated its data bus and control signals allowing another bus master to drive the signals directly.                                                                                                                                                                 |

| NCS<br>(N.C.)                                                                                        | 0           | _             | H(1)<br>R(1)<br>P(1)           | Numerics Coprocessor Select output is generated when accessing a numerics coprocessor. NCS is not provided on the QFP or SQFP packages. This signal does not exist on the 80C188EB/80L188EB.                                                                                                                                                                                                                             |

| ERROR<br>(N.C.)                                                                                      | I           | A(L)          | _                              | ERROR input that indicates the last numerics coprocessor operation resulted in an exception condition. An interrupt TYPE 16 is generated if ERROR is sampled active at the beginning of a numerics operation. ERROR is not provided on the QFP or SQFP packages. This signal does not exist on the 80C188EB/80L188EB.                                                                                                    |

| PEREQ<br>(N.C.)                                                                                      | ı           | A(L)          | _                              | CoProcessor REQuest signals that a data transfer between an External Numerics Coprocessor and Memory is pending. PEREQ is not provided on the QFP or SQFP packages. This signal does not exist on the 80C188EB/80L188EB.                                                                                                                                                                                                 |

| UCS                                                                                                  | 0           | _             | H(1)<br>R(1)<br>P(1)           | Upper Chip Select will go active whenever the address of a memory or I/O bus cycle is within the address limitations programmed by the user. After reset, UCS is configured to be active for memory accesses between 0FFC00H and 0FFFFFH.                                                                                                                                                                                |

| <u>LCS</u>                                                                                           | 0           | _             | H(1)<br>R(1)<br>P(1)           | <b>Lower Chip Select</b> will go active whenever the address of a memory bus cycle is within the address limitations programmed by the user. $\overline{\text{LCS}}$ is inactive after a reset.                                                                                                                                                                                                                          |

| P1.0/GCS0<br>P1.1/GCS1<br>P1.2/GCS2<br>P1.3/GCS3<br>P1.4/GCS4<br>P1.5/GCS5<br>P1.6/GCS6<br>P1.7/GCS7 | 0           | _             | H(X)/H(1)<br>R(1)<br>P(X)/P(1) | These pins provide a multiplexed function. If enabled, each pin can provide a <b>Generic Chip Select</b> output which will go active whenever the address of a memory or I/O bus cycle is within the address limitations programmed by the user. When not programmed as a Chip-Select, each pin may be used as a general purpose output <b>Port.</b> As an output port pin, the value of the pin can be read internally. |

#### NOTE:

Pin names in parentheses apply to the 80C188EB/80L188EB.

Table 3. Pin Descriptions (Continued)

| Pin<br>Name              | Pin<br>Type | Input<br>Type | Output<br>States                                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                  |

|--------------------------|-------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T0OUT<br>T1OUT           | 0           | _             | H(Q)<br>R(1)<br>P(Q)                                                                                                                                                                                                                                                                                | Timer OUTput pins can be programmed to provide a single clock or continuous waveform generation, depending on the timer mode selected.                                                                                                                       |

| TOIN<br>T1IN             | I           | A(L)<br>A(E)  | _                                                                                                                                                                                                                                                                                                   | Timer INput is used either as clock or control signals, depending on the timer mode selected.                                                                                                                                                                |

| INTO<br>INT1<br>INT4     | ı           | A(E,L)        | _                                                                                                                                                                                                                                                                                                   | Maskable <b>INTerrupt</b> input will cause a vector to a specific Type interrupt routine. To allow interrupt expansion, INT0 and/or INT1 can be used with INTA0 and INTA1 to interface with an external slave controller.                                    |

| INT2/INTA0<br>INT3/INTA1 | 1/0         | A(E,L)        | H(1) R(Z) P(1) These pins provide a multiplexed function. As i they provide a maskable INTerrupt that will can the CPU to vector to a specific Type interrupt reads as outputs, each is programmatically controlled provide an INTERRUPT ACKNOWLEDGE handshake signal to allow interrupt expansion. |                                                                                                                                                                                                                                                              |

| P2.7<br>P2.6             | 1/0         | A(L)          | H(X)<br>R(Z)<br>P(X)                                                                                                                                                                                                                                                                                | BI-DIRECTIONAL, open-drain <b>Port</b> pins.                                                                                                                                                                                                                 |

| CTSO<br>P2.4/CTS1        | I           | A(L)          | Clear-To-Send input is used to prevent the transmission of serial data on their respective signal pin. CTS1 is multiplexed with an input function.                                                                                                                                                  |                                                                                                                                                                                                                                                              |

| TXD0<br>P2.1/TXD1        | 0           | _             | H(X)/H(Q)<br>R(1)<br>P(X)/P(Q)                                                                                                                                                                                                                                                                      | Transmit Data output provides serial data information. TXD1 is multiplexed with an output only Port function. During synchronous serial communications, TXD will function as a clock output.                                                                 |

| RXD0<br>P2.0/RXD1        | 1/0         | A(L)          | R(Z)<br>H(Q)<br>P(X)                                                                                                                                                                                                                                                                                | Receive Data input accepts serial data information. RXD1 is multiplexed with an input only Port function. During synchronous serial communications, RXD is bi-directional and will become an output for transmission or data (TXD becomes the clock).        |

| P2.5/BCLK0<br>P2.2/BCLK1 | I           | A(L)/A(E)     | _                                                                                                                                                                                                                                                                                                   | Baud CLock input can be used as an alternate clock source for each of the integrated serial channels.  BCLKx is multiplexed with an input only Port function, and cannot exceed a clock rate greater than one-half the operating frequency of the processor. |

| P2.3/SINT1               | 0           | _             | H(X)/H(Q)<br>R(0)<br>P(X)/P(X)                                                                                                                                                                                                                                                                      | Serial INTerrupt output will go active to indicate serial channel 1 requires service. SINT1 is multiplexed with an output only Port function.                                                                                                                |

**NOTE:** Pin names in parentheses apply to the 80C188EB/80L188EB.

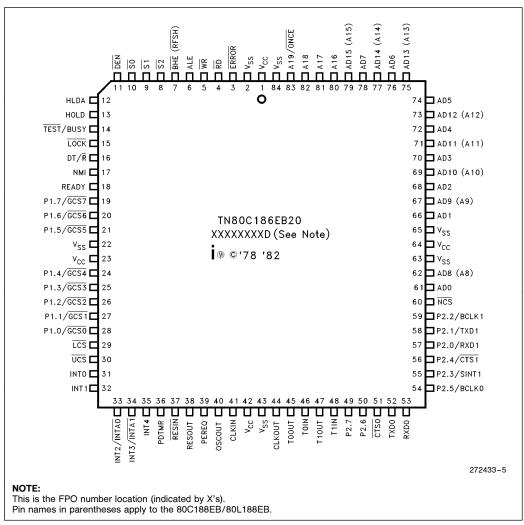

#### **80C186EB PINOUT**

Tables 4 and 5 list the 80C186EB/80C188EB pin names with package location for the 84-pin Plastic Leaded Chip Carrier (PLCC) component. Figure 5 depicts the complete 80C186EB/80C188EB pinout (PLCC package) as viewed from the top side of the component (i.e., contacts facing down).

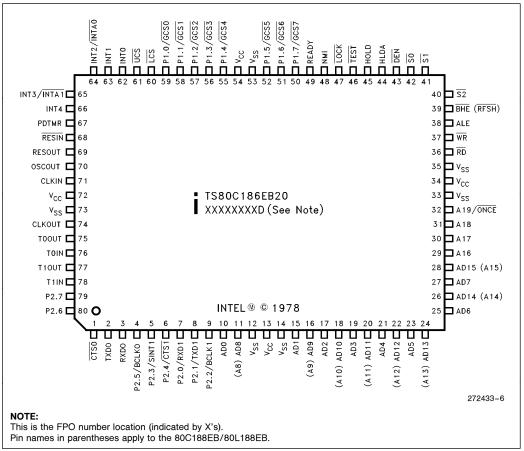

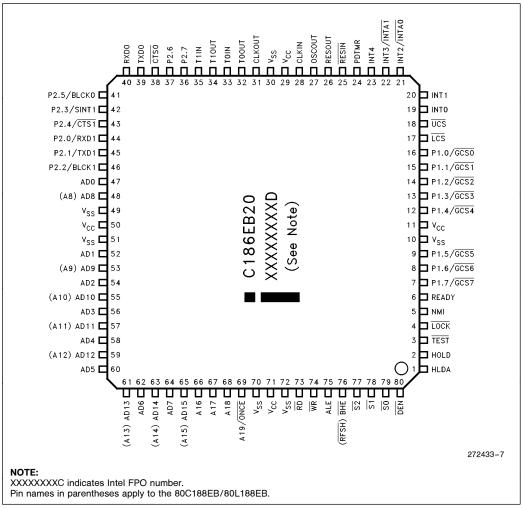

Tables 6 and 7 list the 80C186EB/80C188EB pin names with package location for the 80-pin Quad Flat Pack (QFP) component. Figure 6 depicts the complete 80C186EB/80C188EB (QFP package) as viewed from the top side of the component (i.e., contacts facing down).

Tables 8 and 9 list the 80186EB/80188EB pin names with package location for the 80-pin Shrink Quad Flat Pack (SQFP) component. Figure 7 depicts the complete 80C186EB/80C188EB (SQFP package) as viewed from the top side of the component (i.e., contacts facing down).

Table 4. PLCC Pin Names with Package Location

| Address/Data Bus |          |  |

|------------------|----------|--|

| Name             | Location |  |

| AD0              | 61       |  |

| AD1              | 66       |  |

| AD2              | 68       |  |

| AD3              | 70       |  |

| AD4              | 72       |  |

| AD5              | 74       |  |

| AD6              | 76       |  |

| AD7              | 78       |  |

| AD8 (A8)         | 62       |  |

| AD9 (A9)         | 67       |  |

| AD10 (A10)       | 69       |  |

| AD11 (A11)       | 71       |  |

| AD12 (A12)       | 73       |  |

| AD13 (A13)       | 75       |  |

| AD14 (A14)       | 77       |  |

| AD15 (A15)       | 79       |  |

| A16              | 80       |  |

| A17              | 81       |  |

| A18              | 82       |  |

| A19/ONCE         | 83       |  |

| Table 4. FLCC Fill Nam |          |  |  |  |

|------------------------|----------|--|--|--|

| Bus Control            |          |  |  |  |

| Name                   | Location |  |  |  |

| ALE                    | 6        |  |  |  |

| BHE (RFSH)             | 7        |  |  |  |

| <u>50</u>              | 10       |  |  |  |

| <u>S1</u>              | 9        |  |  |  |

| <u>S2</u>              | 8        |  |  |  |

| RD                     | 4        |  |  |  |

| WR                     | 5        |  |  |  |

| READY                  | 18       |  |  |  |

| DEN                    | 11       |  |  |  |

| DT/R                   | 16       |  |  |  |

| LOCK                   | 15       |  |  |  |

| HOLD                   | 13       |  |  |  |

| HLDA                   | 12       |  |  |  |

| Power           |                         |  |  |

|-----------------|-------------------------|--|--|

| Name            | Location                |  |  |

| V <sub>SS</sub> | 2, 22, 43<br>63, 65, 84 |  |  |

| $V_{CC}$        | 1, 23<br>42, 64         |  |  |

| Processor Control |          |  |

|-------------------|----------|--|

| Name              | Location |  |

| RESIN             | 37       |  |

| RESOUT            | 38       |  |

| CLKIN             | 41       |  |

| OSCOUT            | 40       |  |

| CLKOUT            | 44       |  |

| TEST/BUSY         | 14       |  |

| NCS (N.C.)        | 60       |  |

| PEREQ (N.C.)      | 39       |  |

| ERROR (N.C.)      | 3        |  |

| PDTMR             | 36       |  |

| NMI               | 17       |  |

| INT0              | 31       |  |

| INT1              | 32       |  |

| INT2/INTA0        | 33       |  |

| INT3/INTA1        | 34       |  |

| INT4              | 35       |  |

| 1/0            |          |  |

|----------------|----------|--|

| Name           | Location |  |

| <del>UCS</del> | 30       |  |

| <u>LCS</u>     | 29       |  |

| P1.0/GCS0      | 28       |  |

| P1.1/GCS1      | 27       |  |

| P1.2/GCS2      | 26       |  |

| P1.3/GCS3      | 25       |  |

| P1.4/GCS4      | 24       |  |

| P1.5/GCS5      | 21       |  |

| P1.6/GCS6      | 20       |  |

| P1.7/GCS7      | 19       |  |

| T0OUT          | 45       |  |

| TOIN           | 46       |  |

| T1OUT          | 47       |  |

| T1IN           | 48       |  |

| RXD0           | 53       |  |

| TXD0           | 52       |  |

| P2.5/BCLK0     | 54       |  |

| CTS0           | 51       |  |

| P2.0/RXD1      | 57       |  |

| P2.1/TXD1      | 58       |  |

| P2.2/BCLK1     | 59       |  |

| P2.3/SINT1     | 55       |  |

| P2.4/CTS1      | 56       |  |

| P2.6           | 50       |  |

| P2.7           | 49       |  |

#### NOTE:

Pin names in parentheses apply to the 80C188EB/80L188EB.

Table 5. PLCC Package Locations with Pin Name

| Table 5. FLOO Fackage Locations with Fill Name |                 |          |                 |  |          |                 |          |                 |

|------------------------------------------------|-----------------|----------|-----------------|--|----------|-----------------|----------|-----------------|

| Location                                       | Name            | Location | Name            |  | Location | Name            | Location | Name            |

| 1                                              | V <sub>CC</sub> | 22       | $V_{SS}$        |  | 43       | $V_{SS}$        | 64       | V <sub>CC</sub> |

| 2                                              | V <sub>SS</sub> | 23       | V <sub>CC</sub> |  | 44       | CLKOUT          | 65       | V <sub>SS</sub> |

| 3                                              | ERROR (N.C.)    | 24       | P1.4/GCS4       |  | 45       | T0OUT           | 66       | AD1             |

| 4                                              | RD              | 25       | P1.3/GCS3       |  | 46       | TOIN            | 67       | AD9 (A9)        |

| 5                                              | WR              | 26       | P1.2/GCS2       |  | 47       | T1OUT           | 68       | AD2             |

| 6                                              | ALE             | 27       | P1.1/GCS1       |  | 48       | T1IN            | 69       | AD10 (A10)      |

| 7                                              | BHE (RFSH)      | 28       | P1.0/GCS0       |  | 49       | P2.7            | 70       | AD3             |

| 8                                              | <u>S2</u>       | 29       | <u>LCS</u>      |  | 50       | P2.6            | 71       | AD11 (A11)      |

| 9                                              | S1              | 30       | <del>UCS</del>  |  | 51       | CTS0            | 72       | AD4             |

| 10                                             | <u>50</u>       | 31       | INT0            |  | 52       | TXD0            | 73       | AD12 (A12)      |

| 11                                             | DEN             | 32       | INT1            |  | 53       | RXD0            | 74       | AD5             |

| 12                                             | HLDA            | 33       | INT2/INTA0      |  | 54       | P2.5/BCLK0      | 75       | AD13 (A13)      |

| 13                                             | HOLD            | 34       | INT3/INTA1      |  | 55       | P2.3/SINT1      | 76       | AD6             |

| 14                                             | TEST/BUSY       | 35       | INT4            |  | 56       | P2.4/CTS1       | 77       | AD14 (A14)      |

| 15                                             | LOCK            | 36       | PDTMR           |  | 57       | P2.0/RXD1       | 78       | AD7             |

| 16                                             | DT/R            | 37       | RESIN           |  | 58       | P2.1/TXD1       | 79       | AD15 (A15)      |

| 17                                             | NMI             | 38       | RESOUT          |  | 59       | P2.2/BCLK1      | 80       | A16             |

| 18                                             | READY           | 39       | PEREQ (N.C.)    |  | 60       | NCS (N.C.)      | 81       | A17             |

| 19                                             | P1.7/GCS7       | 40       | OSCOUT          |  | 61       | AD0             | 82       | A18             |

| 20                                             | P1.6/GCS6       | 41       | CLKIN           |  | 62       | AD8 (A8)        | 83       | A19/ONCE        |

| 21                                             | P1.5/GCS5       | 42       | V <sub>CC</sub> |  | 63       | V <sub>SS</sub> | 84       | V <sub>SS</sub> |

**NOTE:** Pin names in parentheses apply to the 80C188EB/80L188EB.

Figure 4. 84-Pin Plastic Leaded Chip Carrier Pinout Diagram

Table 6. QFP Pin Name with Package Location

| Address/Data Bus |          |  |  |

|------------------|----------|--|--|

| Name             | Location |  |  |

| AD0              | 10       |  |  |

| AD1              | 15       |  |  |

| AD2              | 17       |  |  |

| AD3              | 19       |  |  |

| AD4              | 21       |  |  |

| AD5              | 23       |  |  |

| AD6              | 25       |  |  |

| AD7              | 27       |  |  |

| AD8 (A8)         | 11       |  |  |

| AD9 (A9)         | 16       |  |  |

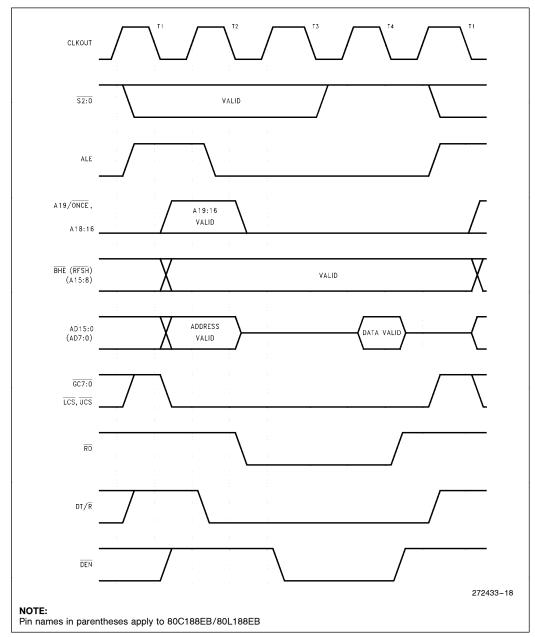

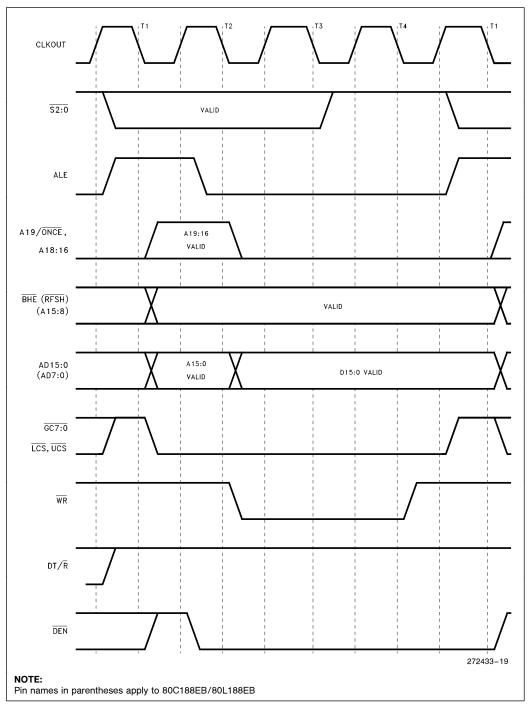

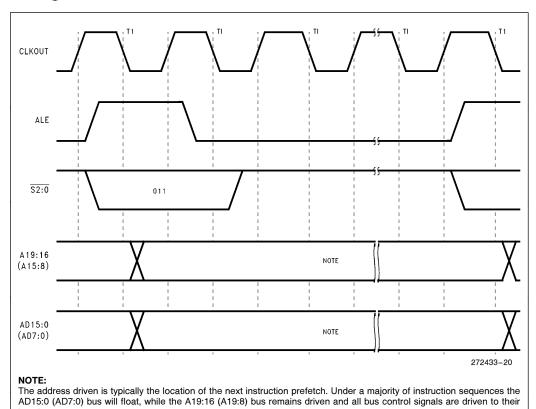

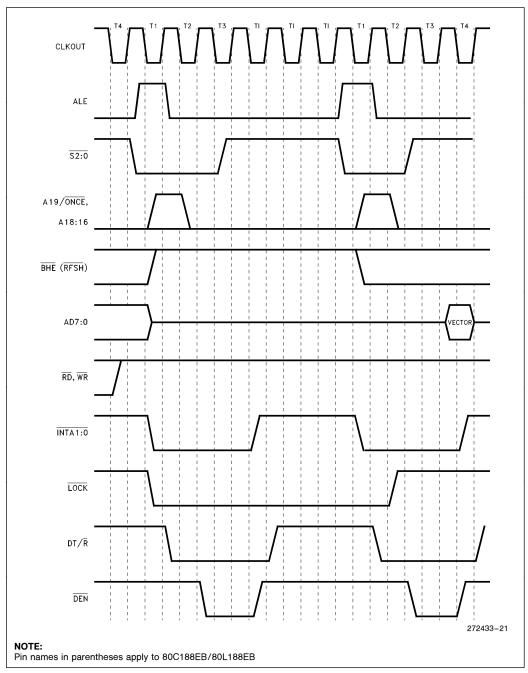

| AD10 (A10)       | 18       |  |  |