intel

iAPX 86,88 User's Manual

**MCS-86**

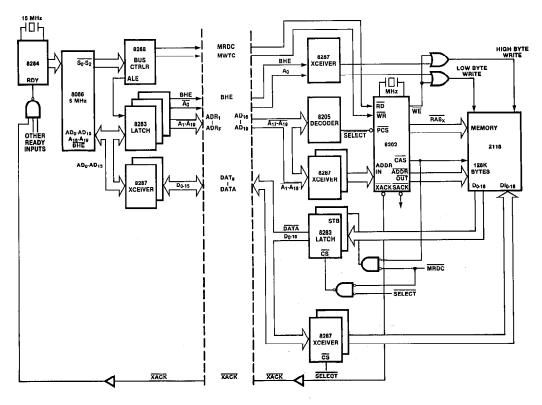

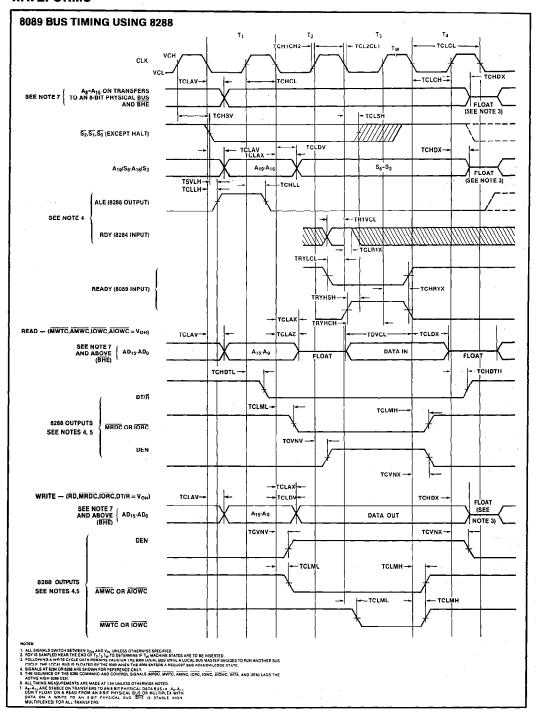

8086 - 8088 - 80C86 - 80C88

Ceibo In-Circuit Emulator Supporting MCS-86: **DS-186**

http://ceibo.com/eng/products/ds186.shtml

| APPENDIX A  Application Notes  AP-67 8086 System Design | APPENDIX B  Device Specifications  iAPX 86/10                                                                                                                                                            |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | ICE 86/88A B-165                                                                                                                                                                                         |

|                                                         | SUPPLEMENT  iAPX 86/20, 88/20 Numerics Supplement  Table of Contents  Processor Overview .5-1  Processor Architecture .5-7  Computation Fundamentals .5-11  Memory .5-21  Multiprocessing Features .5-22 |

Processor Control and Monitoring S-26 Instruction Set S-29 Programming Facilities S-58

| iAPX 86/20, 88/20 Numerics Supplement (Continued)     A-2. Machine Instruction Decoding Guide       Special Topics     S-66       Programming Examples     S-82       86/20, 88/20 Device Specifications     S-89       Tables     S-2       S-1 8087/Emulator Speed     Performance       Comparison     S-3       S-2 Data Types     S-6       S-7 Principal Instructions     S-6       S-7 Register Structure | S-2 S-2 S-7 S-8 S-9 S-10 S-12 S-12 S-14      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

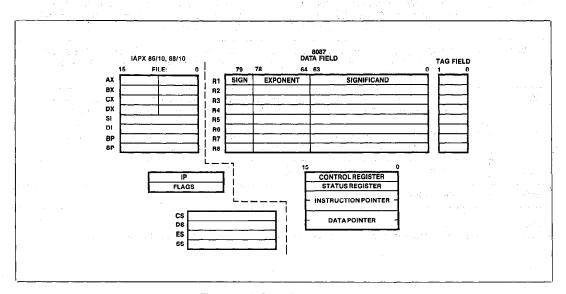

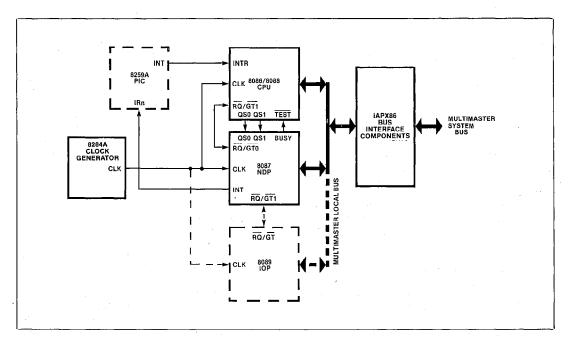

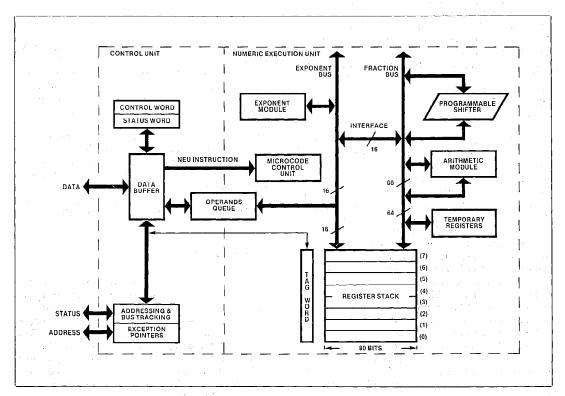

| Special Topics S-66 Programming Examples S-82 86/20, 88/20 Device Specifications S-89 Tables S-1 8087/Emulator Speed Performance Performance Performance S-2 Data Types S-6 S-6 S-4 8087 Block Diagram S-5 Register Structure                                                                                                                                                                                    | S-2S-2S-7S-8S-9S-11S-12S-12S-13              |

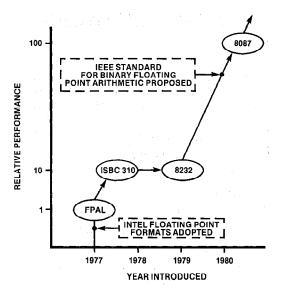

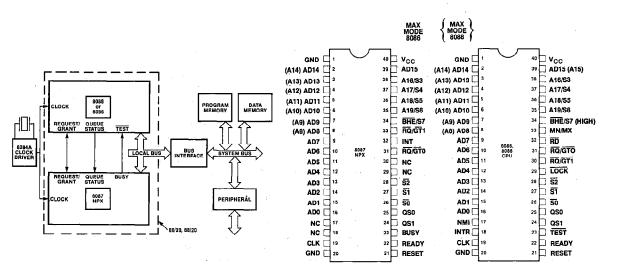

| Programming Examples S-82 86/20, 88/20 Device Specifications S-89 Pin Diagram S-2 8087 Evolution and Relative Performance S-2 Data Types S-6 S-7 Principal Instructions S-80 S-80 Register Structure S-8087 Numeric Data Processor Pin Diagram S-2 8087 Evolution and Relative Performance S-2 NDP Interconnect S-3 NDP Interconnect S-3 Register Structure S-5 Register Structure                               | S-2 S-7 S-8 S-9 S-10 S-12 S-12 S-12 S-14     |

| 86/20, 88/20 Device Specifications       S-89       Pin Diagram         Tables       S-2       8087 Evolution and Relative         S-1       8087/Emulator Speed       Performance         Comparison       S-3       S-3         S-2       Data Types       S-6         S-3       Principal Instructions       S-6         S-5       Register Structure                                                         | S-2 S-7 S-8 S-9 S-10 S-12 S-12 S-12 S-14     |

| Tables         S-2         8087 Evolution and Relative           S-1         8087/Emulator Speed         Performance           Comparison         S-3         S-3         NDP Interconnect           S-2         Data Types         S-6         S-4         8087 Block Diagram           S-3         Principal Instructions         S-6         S-5         Register Structure                                   | S-2 S-7 S-8 S-9 S-10 S-12 S-12 S-12 S-14     |

| S-1         8087/Emulator Speed         Performance           Comparison         S-3         S-3         NDP Interconnect           S-2         Data Types         S-6         S-4         8087 Block Diagram           S-3         Principal Instructions         S-6         S-5         Register Structure                                                                                                    | S-7 S-8 S-9 S-10 S-11 S-12 S-12 S-14         |

| ComparisonS-3S-3NDP InterconnectS-2Data TypesS-6S-48087 Block DiagramS-3Principal InstructionsS-6S-5Register Structure                                                                                                                                                                                                                                                                                           | S-7 S-8 S-9 S-10 S-11 S-12 S-12 S-14         |

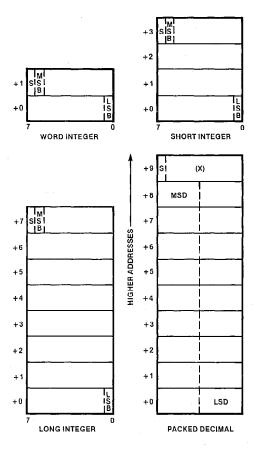

| S-2 Data Types S-6 S-4 8087 Block Diagram S-3 Principal Instructions S-6 S-5 Register Structure                                                                                                                                                                                                                                                                                                                  | S-8<br>S-9<br>S-10<br>S-11<br>S-12<br>S-13   |

| S-3 Principal Instructions                                                                                                                                                                                                                                                                                                                                                                                       | S-9<br>S-10<br>S-11<br>S-12<br>S-13<br>S-14  |

| S-3 Principal Instructions                                                                                                                                                                                                                                                                                                                                                                                       | S-10<br>S-11<br>S-12<br>S-12<br>S-13<br>S-14 |

|                                                                                                                                                                                                                                                                                                                                                                                                                  | S-11<br>S-12<br>S-12<br>S-13                 |

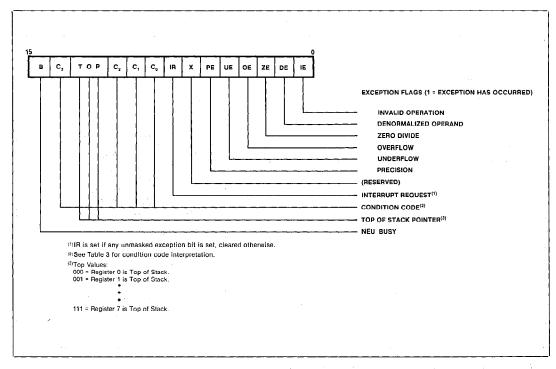

| S-4 Real Number Notation S-15 S-6 Status Word Format                                                                                                                                                                                                                                                                                                                                                             | S-12<br>S-12<br>S-13<br>S-13                 |

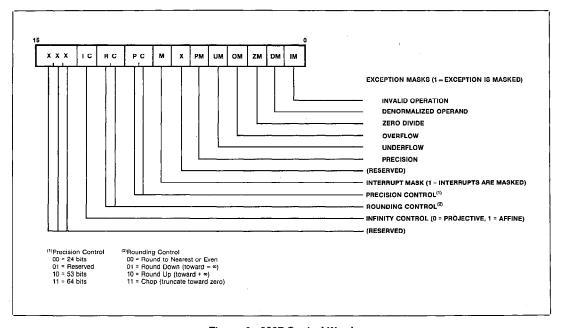

| S-5 Rounding Modes                                                                                                                                                                                                                                                                                                                                                                                               | S-12<br>S-13<br>S-14                         |

| S-6 Exception and Response S-8 Tag Word Format                                                                                                                                                                                                                                                                                                                                                                   | S-13<br>S-14                                 |

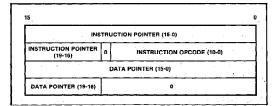

| Summary S-20 S-9 Exception Pointers Format                                                                                                                                                                                                                                                                                                                                                                       | S-14                                         |

| S-7 Processor State S-10 8087 Number System                                                                                                                                                                                                                                                                                                                                                                      |                                              |

| Following Initialization                                                                                                                                                                                                                                                                                                                                                                                         | S-18                                         |

| S-8 Bus Cycle Status Signals S-28 S-12 Projective Versus Affine                                                                                                                                                                                                                                                                                                                                                  | S-18                                         |

| S-9 Data Transfer Instructions S-30 Closure                                                                                                                                                                                                                                                                                                                                                                      |                                              |

| S-10 Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                                                                     | S-21                                         |

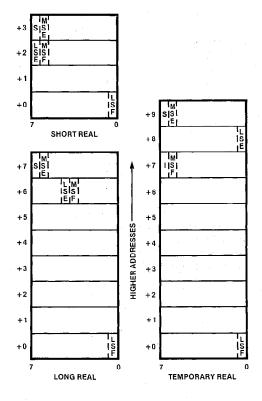

| S-11 Basic Arithmetic Instructions S-14 Storage of Real Data Types                                                                                                                                                                                                                                                                                                                                               | S-21                                         |

| and Operands                                                                                                                                                                                                                                                                                                                                                                                                     |                                              |

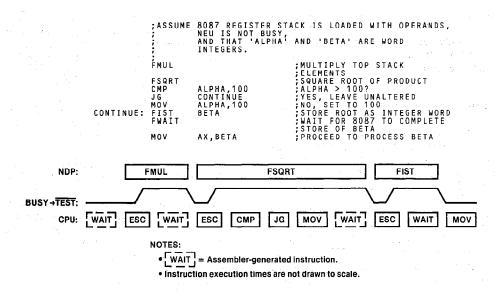

| S-12 Comparison InstructionsS-36 With WAIT                                                                                                                                                                                                                                                                                                                                                                       | S-24                                         |

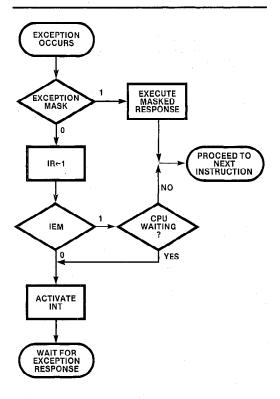

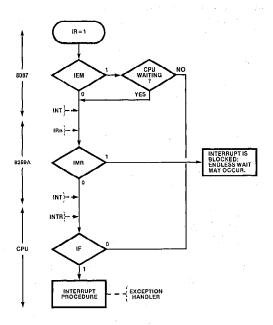

| S-13 FXAM Condition Code Setting S-37 S-16 Interrupt Request Logic                                                                                                                                                                                                                                                                                                                                               | S-27                                         |

| S-14 Transcendental Instructions S-37 S-17 Interrupt Request Path                                                                                                                                                                                                                                                                                                                                                | S-29                                         |

| S-15 Constant Instructions                                                                                                                                                                                                                                                                                                                                                                                       |                                              |

| S-16 Processor Control Instructions S-39 Layout                                                                                                                                                                                                                                                                                                                                                                  | S-41                                         |

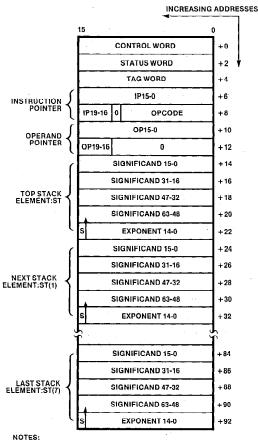

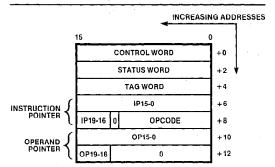

| S-17 Key to Operand TypesS-42 S-19 FSTENV/FLDENV Memory                                                                                                                                                                                                                                                                                                                                                          |                                              |

| S-18 Execution PenaltiesS-43 Layout                                                                                                                                                                                                                                                                                                                                                                              | S-41                                         |

| S-19 Instruction Set S-20 Sample 8087 Constants                                                                                                                                                                                                                                                                                                                                                                  | S-43                                         |

| Reference Data                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| S-20 PL/M-86 Built-in Procedures S-59 Definition                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| S-21 Storage Allocation DirectivesS-60 S-22 Structure Definition                                                                                                                                                                                                                                                                                                                                                 |                                              |

| S-22 Addressing Mode Examples S-62 S-23 Sample PL/M-86 Program                                                                                                                                                                                                                                                                                                                                                   |                                              |

| S-23 Denormalization ProcessS-68 S-24 Sample ASM-86 Program                                                                                                                                                                                                                                                                                                                                                      | S-65                                         |

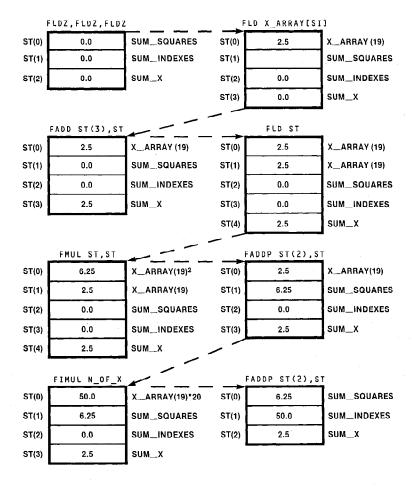

| S-24 Exceptions Due to Denormal S-25 Instructions and Register                                                                                                                                                                                                                                                                                                                                                   |                                              |

| Operands S-69 Stack                                                                                                                                                                                                                                                                                                                                                                                              | S-68                                         |

| S-25 Unnormal Operands and S-26 Conditional Branching                                                                                                                                                                                                                                                                                                                                                            |                                              |

| Results                                                                                                                                                                                                                                                                                                                                                                                                          | S-82                                         |

| S-26 Zero Operands and Results S-71 S-27 Conditional Branching for                                                                                                                                                                                                                                                                                                                                               |                                              |

| S-27 Infinity Operands and Results S-72 FXAM                                                                                                                                                                                                                                                                                                                                                                     |                                              |

| S-28 Binary Integer EncodingsS-75 S-28 Full State Exception Handler                                                                                                                                                                                                                                                                                                                                              |                                              |

| S-29 Packed Decimal Encodings S-76 S-29 Latency Exception Handler                                                                                                                                                                                                                                                                                                                                                | S-87                                         |

| S-30 Real and Long Real S-30 Reentrant Exception Handler                                                                                                                                                                                                                                                                                                                                                         | S-87                                         |

| Encodings S-76                                                                                                                                                                                                                                                                                                                                                                                                   |                                              |

| S-31 Temporary Real Encodings S-77 8087 INSTRUCTIONS, ENCODING                                                                                                                                                                                                                                                                                                                                                   |                                              |

| S-32 Exception Conditions and AND DECODING                                                                                                                                                                                                                                                                                                                                                                       | S-109                                        |

| Masked Responses S-79                                                                                                                                                                                                                                                                                                                                                                                            |                                              |

| S-33 Masked Overflow Response for                                                                                                                                                                                                                                                                                                                                                                                |                                              |

| Directed Rounding S-81                                                                                                                                                                                                                                                                                                                                                                                           |                                              |

# Appendix A Application Notes

## APPENDIX A APPLICATION NOTES

This appendix contains Intel application notes pertinent to the 8086 family microprocessors. The following application notes, in the order listed, have been included within this appendix:

| AP-67  | 8086 System Design                                                                 |

|--------|------------------------------------------------------------------------------------|

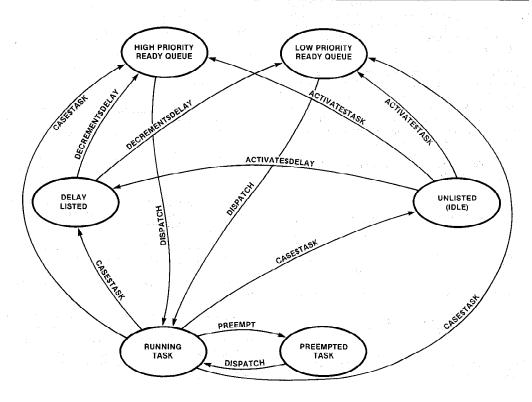

| AP-61  | Multitasking for the 8086                                                          |

| AP-50  | Debugging Strategies and Considerations for 8089 Systems                           |

| AP-51  | Designing 8086, 8088, 8089 Multiprocessing Systems with the 8289 Bus Arbiter       |

| AP-59  | Using the 8259A Programmable Interrupt Controller                                  |

| AP-28A | Intel® Multibus <sup>TM</sup> Interfacing                                          |

| AP-43  | Using the iSBC-957 <sup>TM</sup> Execution Vehicle for Executing 8086 Program Code |

September 1979

8086 System Desidin

### 8086 System Design

#### **Contents**

- 1. INTRODUCTION

- 2. 8086 OVERVIEW AND BASIC SYSTEM CONCEPTS

- A. Bus Cycle Definition

- B. Address and Data Bus Concepts

- C. System Data Bus Concepts

- D. Multiprocessor Environment

- 3. 8086 SYSTEM DETAILS

- A. Operating Modes

- B. Clock Generation

- C. Reset

- D. Ready Implementation and Timing

- E. Interrupt Structure

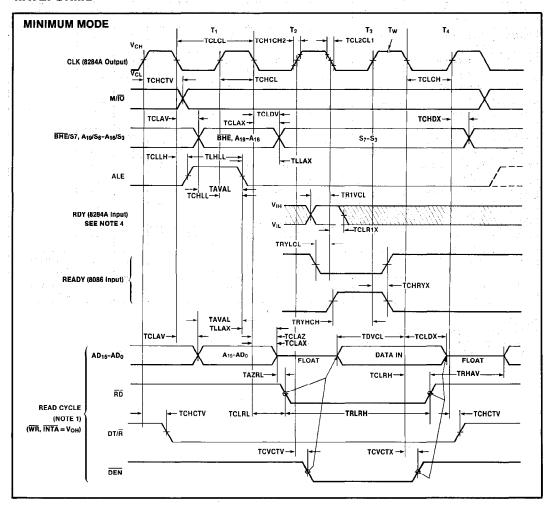

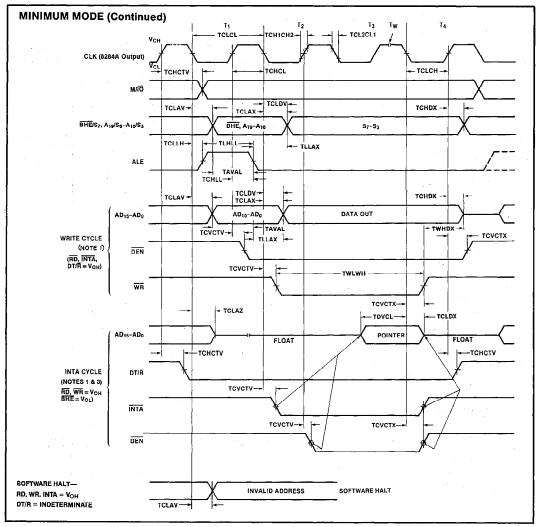

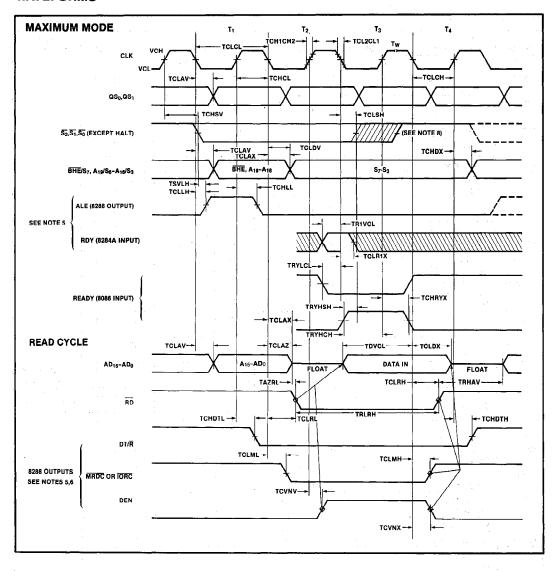

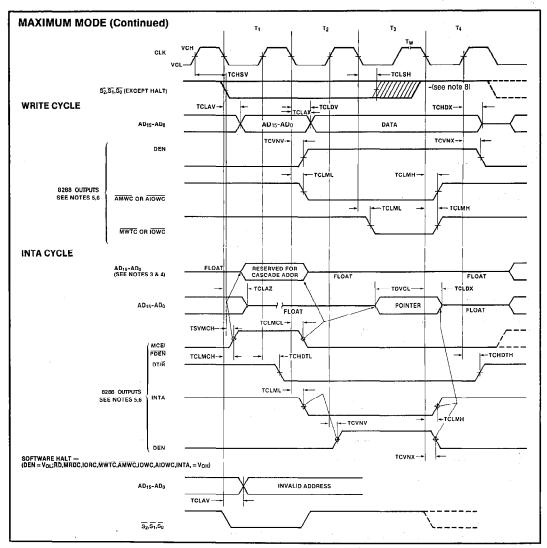

- F. Interpreting the 8086 Bus Timing Diagrams

- G. Bus Control Transfer

- 4. INTERFACING WITH I/O

- 5. INTERFACING WITH MEMORIES

- 6. APPENDIX

#### 1. INTRODUCTION

The 8086 family, Intel's new series of microprocessors and system components, offers the designer an advanced system architecture which can be structured to satisfy a broad range of applications. The variety of speed, configuration and component selections available within the family enables optimization of a specific design to both cost and performance objectives. More important however, the 8086 family concept allows the designer to develop a family of systems providing multiple levels of enhancement within a single design and a growth path for future designs.

This application note is directed toward the implementation of the system hardware and will provide an introduction to a representative sample of the systems configurable with the 8086 CPU member of the family. Application techniques and timing analysis will be given to aid the designer in understanding the system requirements, advantages and limitations. Additional Intel publications the reader may wish to reference are the 8086 User's Manual (9800722A), 8086 Assembly Lan-

guage Reference Guide (9800749A), AP-28A MULTI-BUS<sup>TM</sup> Interfacing (98005876B), INTEL MULTIBUS<sup>TM</sup> SPECIFICATION (9800683), AP-45 Using the 8202 Dynamic RAM Controller (9300809A), AP-51 Designing 8086, 8088, 8089 Multiprocessor Systems with the 8289 Bus Arbiter and AP-59 Using the 8259A Programmable Interrupt Controller. References to other Intel publications will be made throughout this note.

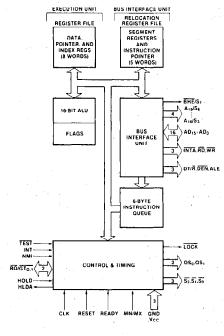

#### 2. 8086 OVERVIEW AND BASIC SYSTEM CONCEPTS

#### 2A. 8086 Bus Cycle Definition

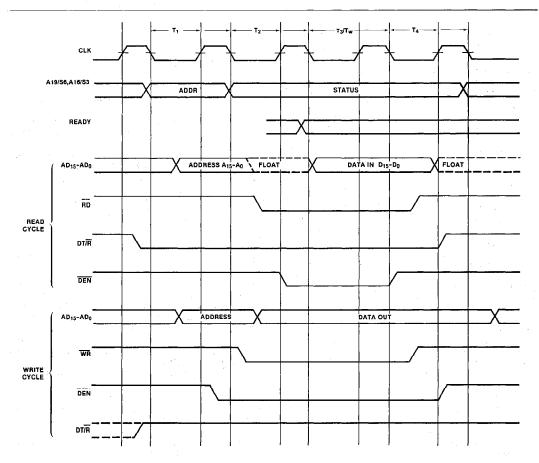

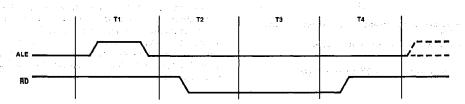

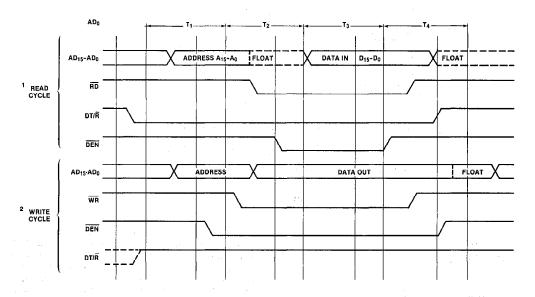

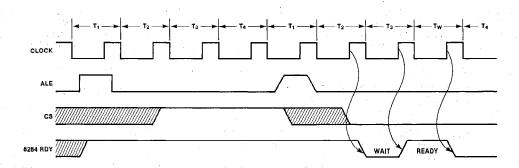

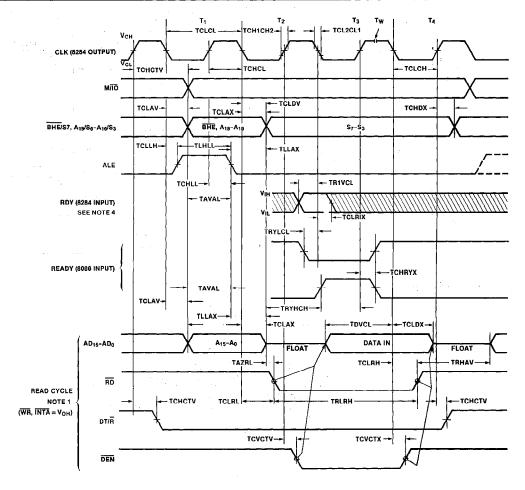

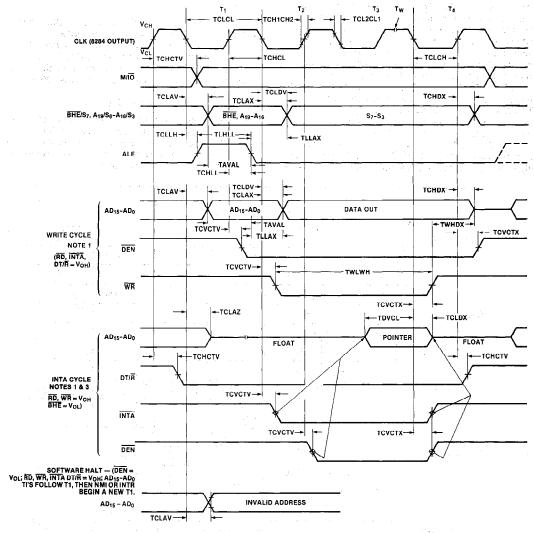

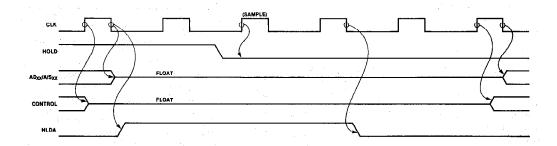

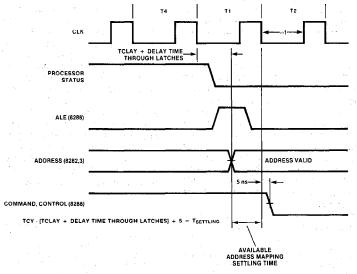

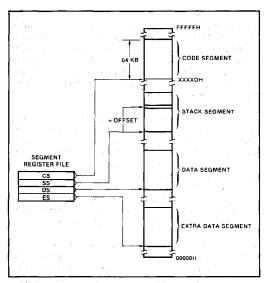

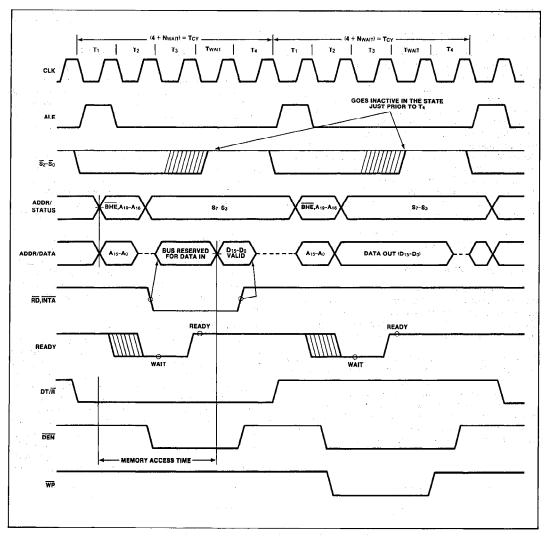

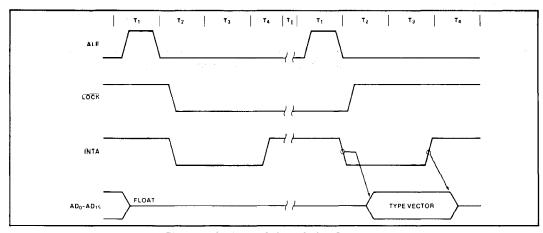

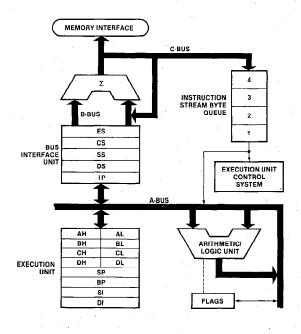

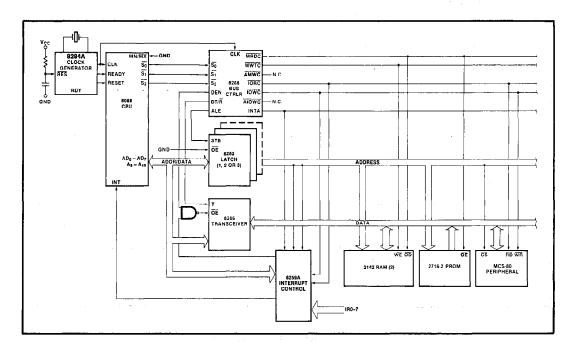

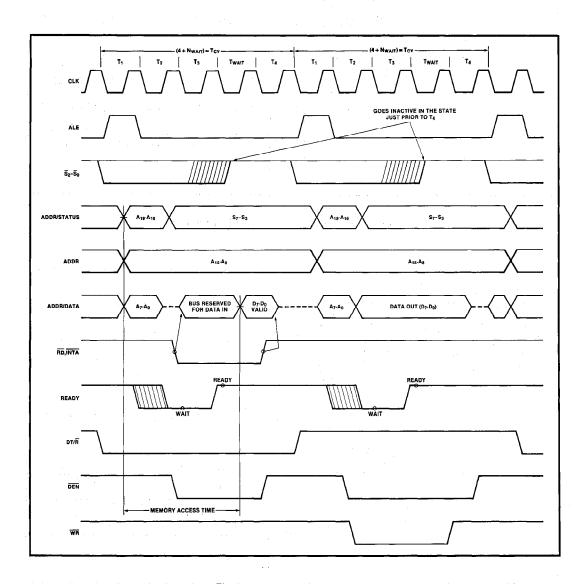

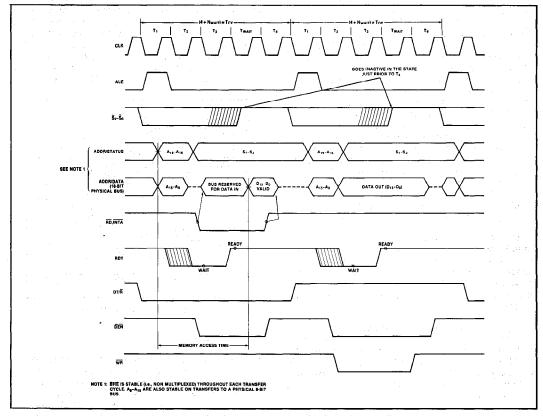

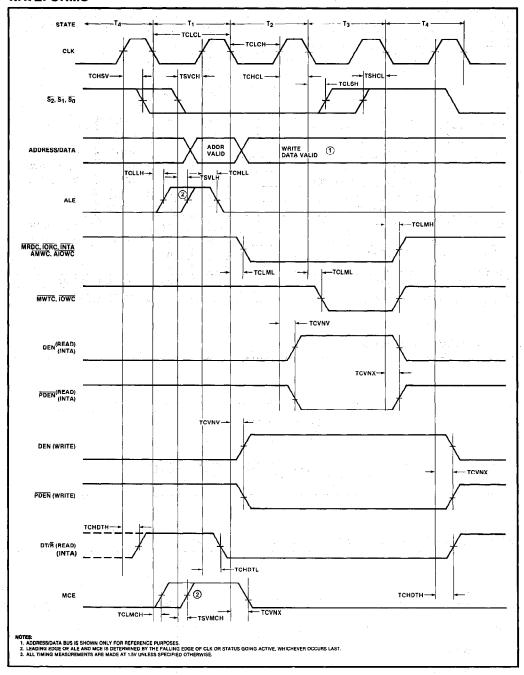

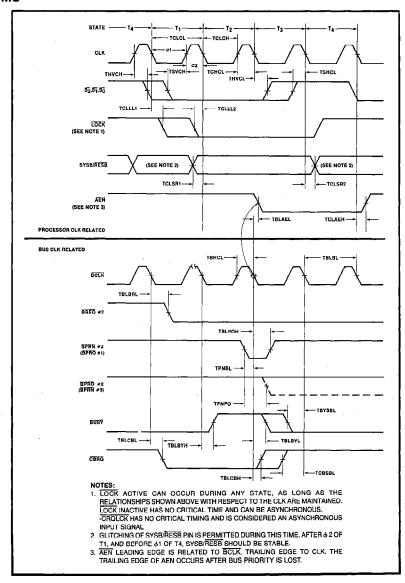

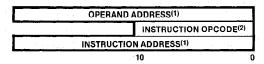

The 8086 is a true 16-bit microprocessor with 16-bit internal and external data paths, one megabyte of memory address space (2\*\*20) and a separate 64K byte (2\*\*16) I/O address space. The CPU communicates with its external environment via a twenty-bit time multiplexed address, status and data bus and a command bus. To transfer data or fetch instructions, the CPU executes a bus cycle (Fig. 2A1). The minimum bus cycle consists of four CPU clock cycles called T states. During the first T state (T1), the CPU asserts an address on the twenty-bit

Figure 2A1. Basic 8086 Bus Cycle

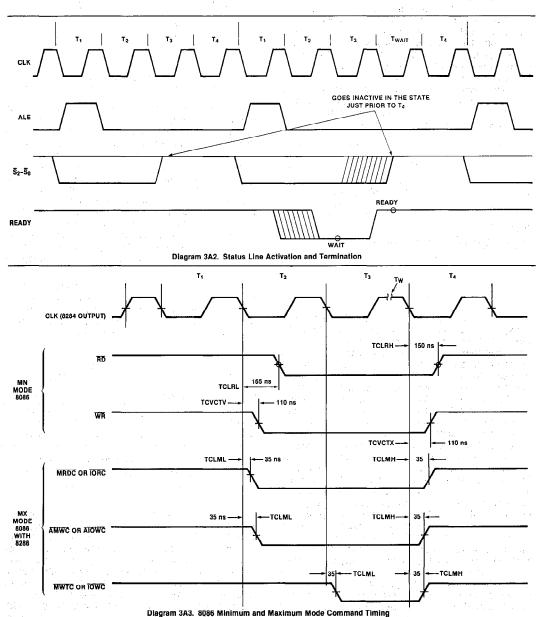

multiplexed address/data/status bus. For the second T state (T2), the CPU removes the address from the bus and either three-states its outputs on the lower sixteen bus lines in preparation for a read cycle or asserts write data. Data bus transceivers are enabled in either T1 or T2 depending on the 8086 system configuration and the direction of the transfer (into or out of the CPU). Read, write or interrupt acknowledge commands are always enabled in T2. The maximum mode 8086 configuration (to be discussed later) also provides a write command enabled in T3 to guarantee data setup time prior to command activation.

During T2, the upper four multiplexed bus lines switch from address. (A19-A16) to bus cycle status (S6,S5,S4,S3). The status information (Table 2A1) is available primarily for diagnostic monitoring. However, a decode of S3 and S4 could be used to select one of four banks of memory, one assigned to each segment register. This technique allows partitioning the memory by segment to expand the memory addressing beyond one megabyte. It also provides a degree of protection by preventing erroneous write operations to one segment from overlapping into another segment and destroying information in that segment.

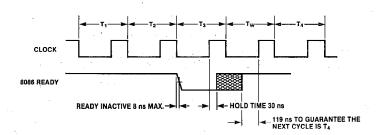

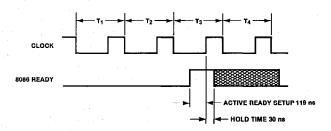

The CPU continues to provide status information on the upper four bus lines during T3 and will either continue to assert write data or sample read data on the lower sixteen bus lines. If the selected memory or I/O device is not capable of transferring data at the maximum CPU transfer rate, the device must signal the CPU "not ready" and force the CPU to Insert additional clock cycles (Wait states TW) after T3. The 'not ready' indication must be presented to the CPU by the start of T3. Bus activity during TW is the same as T3. When the selected device has had sufficient time to complete the transfer, it asserts "Ready" and allows the CPU to continue from the TW states. The CPU will latch the data on the bus during the last wait state or during T3 if no wait states are requested. The bus cycle is terminated in T4 (command lines are disabled and the selected external device deselects from the bus). The bus cycle appears to devices in the system as an asynchronous event consisting of an address to select the device followed by a read strobe or data and a write strobe. The selected device accepts bus data during a write cycle and drives the desired data onto the bus during a read cycle. On termination of the command, the device latches write data or disables its bus drivers. The only control the device has on the bus cycle is the insertion of wait cycles.

The 8086 CPU only executes a bus cycle when Instructions or operands must be transferred to or from memory or I/O devices. When not executing a bus cycle, the bus interface executes idle cycles (TI). During the idle cycles, the CPU continues to drive status information from the previous bus cycle on the upper address lines. If the previous bus cycle was a write, the CPU continues to drive the write data onto the multiplexed bus until the start of the next bus cycle. If the CPU executes idle cycles following a read cycle, the CPU will not drive the lower 16 bus lines until the next bus cycle is required.

Since the CPU prefetches up to six bytes of the instruction stream for storage and execution from an internal instruction queue, the relationship of instruction fetch and associated operand transfers may be skewed in time and separated by additional instruction fetch bus cycles. In general, if an instruction is fetched into the 8086's internal instruction queue, several additional instructions may be fetched before the instruction is removed from the queue and executed. If the instruction being executed from the queue is a jump or other control transfer instruction, any instructions remaining in the queue are not executed and are discarded with no effect on the CPU's operation. The bus activity observed during execution of a specific instruction is dependent on the preceding instructions but is always deterministic within the specific sequence.

Table 2A1

|     |            |                                           | 11 24 1         |

|-----|------------|-------------------------------------------|-----------------|

| S3" | <b>S</b> 4 |                                           |                 |

| 0   | 0          | Alternate (relative to                    | the ES segment) |

| 1   | · · · O    | Stack (relative to th                     | e SS segment)   |

| 0   | .1         | Code/None (relative ment or a default     |                 |

| -1  | 1.         | Data (relative to the                     | DS segment)     |

|     |            | t enable flag)<br>s the 8086 is on the bu | ıs)             |

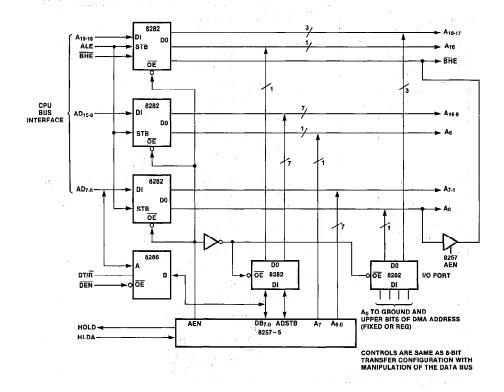

#### 2B. 8086 Address and Data Bus Concepts

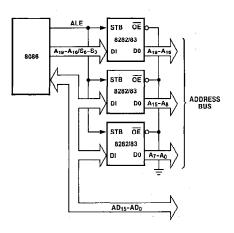

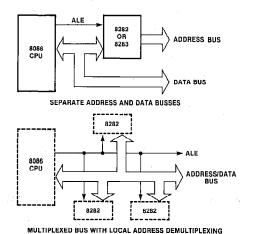

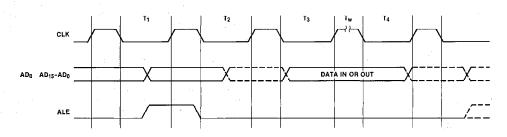

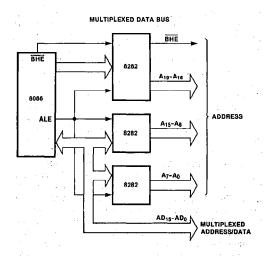

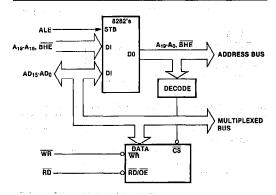

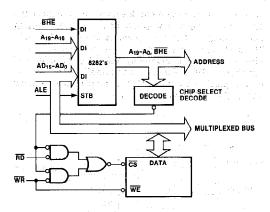

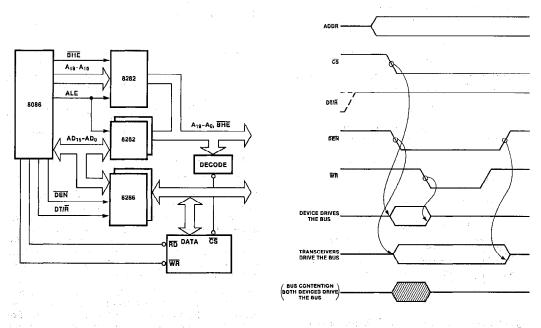

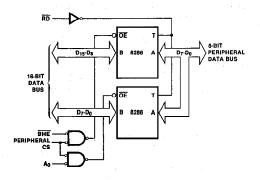

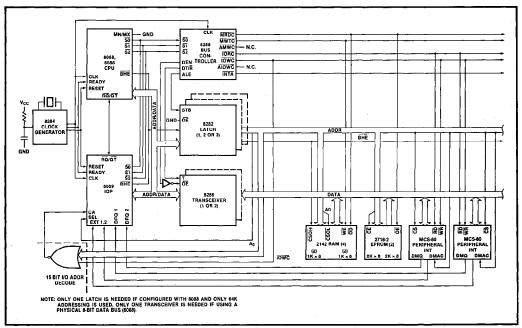

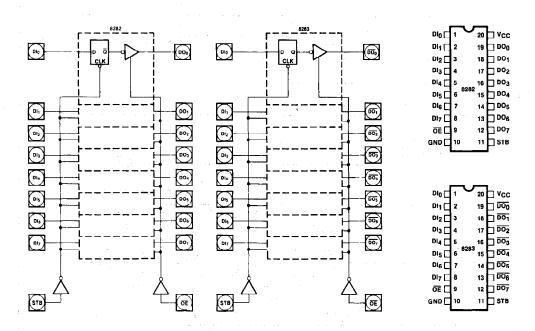

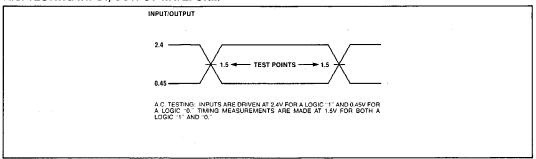

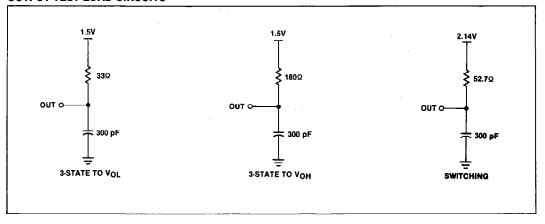

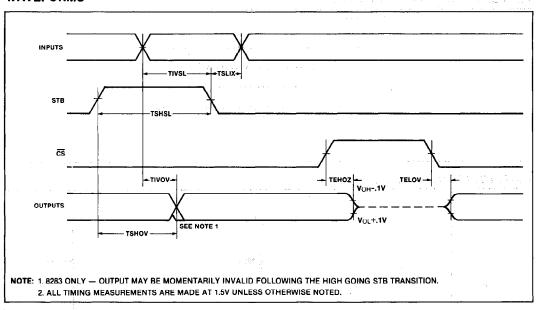

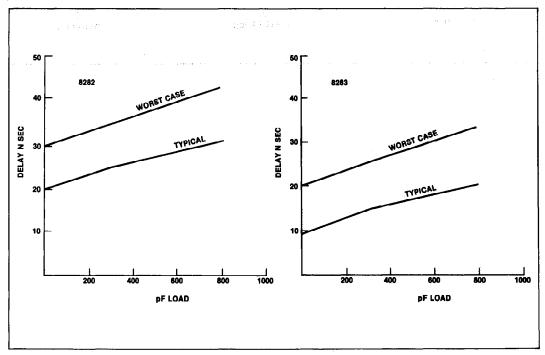

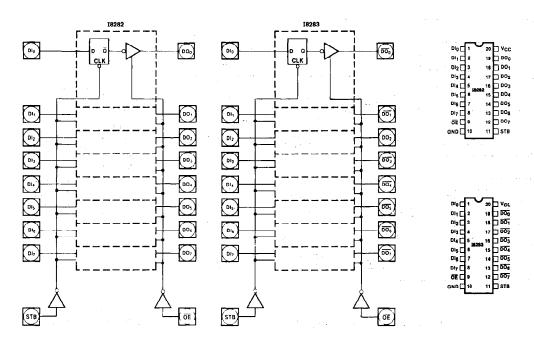

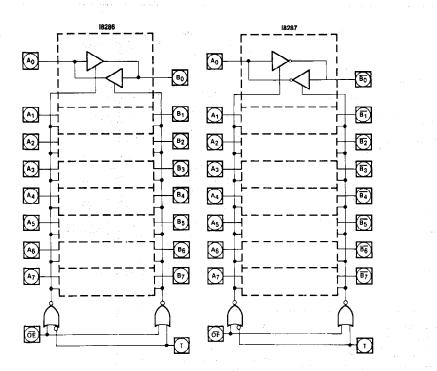

Since the majority of system memories and peripherals require a stable address for the duration of the bus cycle, the address on the multiplexed address/data bus during T1 should be latched and the latched address used to select the desired peripheral or memory location. Since the 8086 has a 16-bit data bus, the multiplexed bus components of the 8085 family are not applicable to the 8086 (a device on address/data bus lines 8-15 will not be able to receive the byte selection address on lines 0-7). To demultiplex the bus (Fig. 2B1a), the 8086 system provides an Address Latch Enable signal (ALE) to capture the address in either the 8282 or 8283 8-bit bi-stable latches (Diag. 2B1). The latches are either inverting (8283) or non-inverting (8282) and have outputs driven by three-state buffers that supply 32 mA drive capability and can switch a 300 pF capacitive load in 22 ns (inverting) or 30 ns (non-inverting). They propagate the address through to the outputs while ALE is high and latch the address on the falling edge of ALE. This only delays address access and chip select decoding by the propagation delay of the latch. The outputs are enabled through the low active OE input. The demultiplexing of the multiplexed address/data bus (latchings of the address from the multiplexed bus), can be done locally at appropriate points in the system or at the CPU with a separate address bus distributing the address throughout the system (Fig. 2B1b). For optimum system performance and compatibility with multiprocessor and MULTIBUSTM configurations, the latter technique is strongly recommended over the first. The remainder of this note will assume the bus is demultiplexed at the CPU.

Figure 2B1a. Demultiplexing the 8086 Bus

Figure 2B1b.

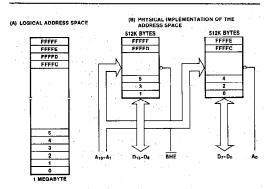

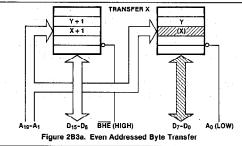

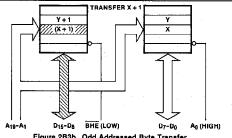

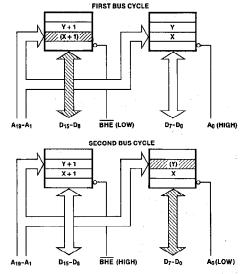

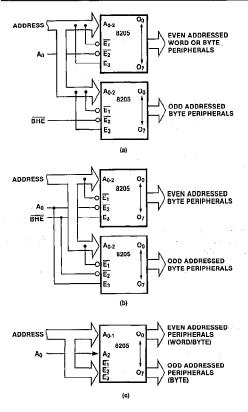

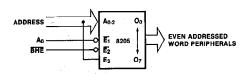

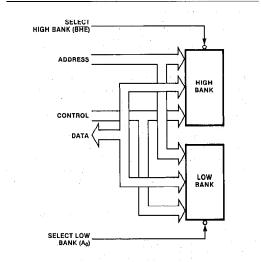

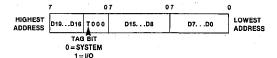

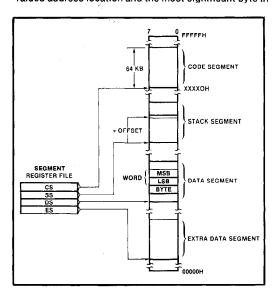

The programmer views the 8086 memory address space as a sequence of one million bytes in which any byte may contain an eight bit data element and any two consecutive bytes may contain a 16-bit data element. There is no constraint on byte or word addresses (boundaries). The address space is physically implemented on a sixteen bit data bus by dividing the address space into two banks of up to 512K bytes (Fig. 2B2). One bank is connected to the lower half of the sixteen-bit data bus (D7-0) and contains even addressed bytes (A0 = 0). The other bank is connected to the upper half of the data bus (D15-8) and contains odd addressed bytes (A0 = 1). A specific byte within each bank is selected by address lines A19-A1. To perform byte transfers to even addresses (Fig. 2B3a), the information is transferred over the lower half of the data bus (D7-0). A0 (active low) is used to enable the bank connected to the lower half of the data bus to participate in the transfer. Another signal provided by the 8086, Bus High Enable (BHE), is used to disable the bank on the upper half of the data bus from participating in the transfer. This is necessary to prevent a write operation to the lower bank from destroying data in the upper bank. Since BHE is a multiplexed signal with timing identical to the A19-A16 address lines, it also should be latched with ALE to provide a stable signal during the bus cycle. During T2 through T4, the BHE output is multiplexed with status line S7 which is equal to BHE. To perform byte transfers to odd addresses (Fig. 2B3b), the information is transferred over the upper half of the data bus (D15-D8) while BHE (active low) enables the upper bank and A0 disables the lower bank. Directing the data transfer to the appropriate half of the data bus and activation of BHE and A0 is performed by the 8086, transparent to the programmer. As an example, consider loading a byte of data into the CL register (lower half of the CX register) from an odd addressed memory location (referenced over the upper half of the 16-bit data bus). The data is transferred into the 8086 over the upper 8 bits of the data bus, automatically redirected to the lower half of the 8086 internal 16-bit data path and stored into the CL register. This capability also allows byte I/O transfers with the AL register to be directed to I/O devices connected to either the upper or lower half of the 16-bit data bus.

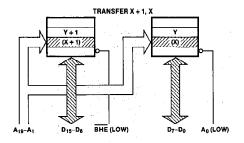

To access even addressed sixteen bit words (two consecutive bytes with the least significant byte at an even

Diagram 2B1. ALE Timing

byte address), A19-A1 select the appropriate byte within each bank and A0 and BHE (active low) enable both banks simultaneously (Fig. 2B3c). To access an odd addressed 16-bit word (Fig. 2B3d), the least significant byte (addressed by A19-A1) is first transferred over the upper half of the bus (odd addressed byte, upper bank, BHE low active and A0 = 1). The most significant byte is accessed by incrementing the address (A19-A0) which allows A19-A1 to address the next physical word location (remember, A0 was equal to one which indicated a word referenced from an odd byte boundary). A second bus cycle is then executed to perform the transfer of the most significant byte with the lower bank (A0 is now active low and BHE is high). The sequence is automatically executed by the 8086 whenever a word transfer is executed to an odd address. Directing the upper and lower bytes of the 8086's internal sixteen-bit registers to the appropriate halves of the data bus is also performed automatically by the 8086 and is transparent to the programmer.

Figure 2B2. 8086 Memory

Figure 2B3b. Odd Addressed Byte Transfer

Figure 2B3c. Even Addressed Word Transfer

Figure 2B3d. Odd Addressed Word Transfer

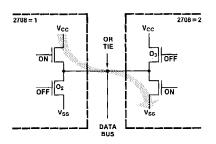

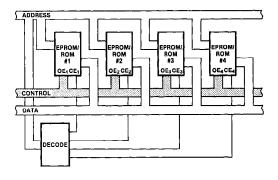

During a byte read, the CPU floats the entire sixteen-bit data bus even though data is only expected on the upper or lower half of the data bus. As will be demonstrated later, this action simplifies the chip select decoding requirements for read only devices (ROM, EPROM). During a byte write operation, the 8086 will drive the entire sixteen-bit data bus. The information on the half of the data bus not transferring data is indeterminate. These concepts also apply to the I/O address space. Specific examples of I/O and memory interfacing are considered in the corresponding sections.

#### 2C. System Data Bus Concepts

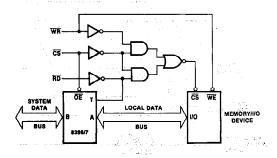

When referring to the system data bus, two implementation alternatives must be considered; (a) the multiplexed address/data bus (Fig. 2C1a) and a data bus buffered from the multiplexed bus by transceivers (Fig. 2C1b).

If memory or I/O devices are connected directly to the multiplexed bus, the designer must guarantee the devices do not corrupt the address on the bus during T1.

Figure 2C1a. Multiplexed Data Bus

BUFFFRED DATA BUS

8282 A<sub>19</sub>-A<sub>16</sub>

8282 A<sub>19</sub>-A<sub>16</sub>

8282 A<sub>15</sub>-A<sub>8</sub>

8282 A<sub>7</sub>-A<sub>0</sub>

8282 A<sub>7</sub>-A<sub>0</sub>

8282 A<sub>15</sub>-A<sub>8</sub>

SYSTEM BUS

DATA

DATA

EN

8286/8287 B

D7-D<sub>0</sub>

T

DATA

Figure 2C1b. Buffered Date Bus

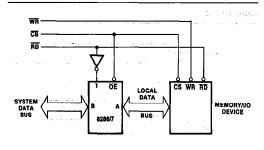

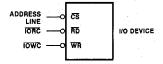

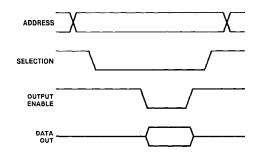

To avoid this, device output drivers should not be enabled by the device chip select, but should have an output enable controlled by the system read signal (Fig. 2C2). The 8086 timing guarantees that read is not valid until after the address is latched by ALE (Diag. 2C1). All Intel peripherals, EPROM products and RAM's for microprocessors provide output enable or read inputs to allow connection to the multiplexed bus.

Figure 2C2. Devices with Output Enables on the Multiplexed Bus

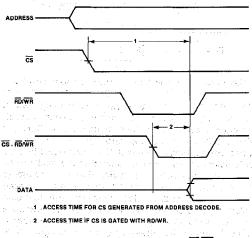

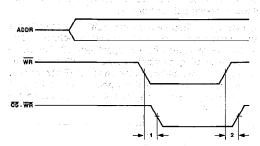

Several techniques are available for interfacing devices without output enables to the multiplexed bus but each introduces other restrictions or limitations. Consider Figure 2C3 which has chip select gated with read and write. Two problems exist with this technique. First, the chip select access time is reduced to the read access time, and may require a faster device if maximum system performance (no wait states) is to be achieved (Diag. 2C2). Second, the designer must verify that chip select to write setup and hold times for the device are not violated (Diag. 2C3). Alternate techniques can be extracted from the bus interfacing techniques given later in this section but are subject to the associated restrictions. In general, the best solution is obtained with devices having output enables.

A subsequent limitation on the multiplexed bus is the 8086's drive capability of 2.0 mA and capacitive loading of 100 pF to guarantee the specified A.C. characteristics. Assuming capacitive loads of 20 pF per I/O device, 12 pF per address latch and 5-12 pF per memory device, a system mix of three peripherals and two to four memory devices (per bus line) are close to the loading limit.

Diagram 2C1. Relationship of ALE to READ

Figure 2C3. Devices without Output Enables on the Multiplexed Bus

Diagram 2C2. Access Time: CS Gated with RD/WR

- 1 CS IS NOT VALID PRIOR TO WRITE AND BECOMES ACTIVE ONE OR TWO GATE DELAYS LATER.

- 2 CS REMAINS VALID AFTER WRITE ONE OR TWO GATE DELAYS.

Diagram 2C3. CS to WR Set-Up and Hold

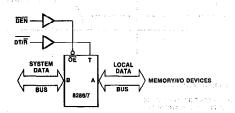

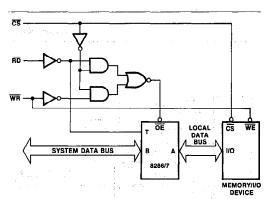

To satisfy the capacitive loading and drive requirements of larger systems, the data bus must be buffered. The 8286 non-inverting and 8287 inverting octal transceivers are offered as part of the 8086 family to satisfy this requirement. They have three-state output buffers that drive 32 mA on the bus interface and 10 mA on the CPU interface and can switch capacitive loads of 300 pF at the bus interface and 100 pF on the CPU interface in 22 ns (8287) or 30 ns (8286). To enable and control the direction of the transceivers, the 8086 system provides Data ENable (DEN) and Data Transmit/Receive (DT/R) signals (Fig. 2C1b). These signals provide the appropriate timing to guarantee isolation of the multiplexed bus from the system during T1 and elimination of bus contention with the CPU during read and write (Diag. 2C4). Although the memory and peripheral devices are isolated from the CPU (Fig. 2C4), bus contention may still exist in the system if the devices do not have an output enable control other than chip select. As an example, bus contention will exist during transition from one chip select to another (the newly selected device begins driving the bus before the previous device has disabled its drivers). Another, more severe case exists during a write cycle. From chip select to write active, a device whose outputs are controlled only by chip select, will drive the bus simultaneously with write data being driven through the transceivers by the CPU (Diag. 2C5). The same technique given for circumventing these problems on the multiplexed bus can be applied here with the same limitations.

One last extension to the bus implementation is a second level of buffering to reduce the total load seen by devices on the system bus (Fig. 2C5). This is typically done for multiboard systems and isolation of memory arrays. The concerns with this configuration are the additional delay for access and more important, control of the second transceiver in relationship to the system bus and the device being interfaced to the system bus. Several techniques for controlling the transceiver are given in Figure 2C6. This first technique (Fig. 2C6a) simply distributes DEN and DT/R throughout the system. DT/R is inverted to provide proper direction control for the second level transceivers. The second example (Fig. 2C6b) provides control for devices with output enables. RD is used to normally direct data from the system bus to the peripheral. The buffer is selected whenever a device on the local bus is chip selected. Bus contention is possible on the device's local bus during a read as the read simultaneously enables the device output and changes the transceiver direction. The contention may also occur as the read is terminated.

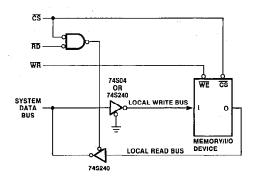

For devices without output enables, the same technique can be applied (Fig. 2C6c) if the chip select to the device is conditioned by read or write. Controlling the chip select with read/write prevents the device from driving against the transceiver prior to the command being received. The limitations with this technique are access limited to read/write time and limited CS to write setup and hold times.

- 1 DEN IS ENABLED AFTER THE 8088 HAS FLOATED THE MULTIPLEXED BUS

- 2 DEN ENABLES THE TRANSCEIVERS EARLY IN THE CYCLE, BUT DTIR QUARANTEES THE TRANSCEIVERS ARE IN TRANSMIT RATHER THAN RECEIVE MODE AND WILL NOT DRIVE AGAINST THE CPU.

#### Diagram 2C4. Bus Transceiver Control

Figure 2C4. Devices with Output Enables on the System Bus

Diagram 2C5.

Figure 2C5. Fully Buffered System

Figure 2C6a. Controlling System Transceivers with DEN and DT/R

Figure 2C6b. Buffering Devices with OE/RD

Figure 2C6c. Buffering Devices without OE/RD and with Common or Separate Input/Output

An alternate technique applicable to devices with and without output enables is shown in Figure 2C6d. RD again controls the direction of the transceiver but it is not enabled until a command and chip select are active. The possibility for bus contention still exists but is reduced to variations in output enable vs. direction change time for the transceiver. Full access time from chip select is now available, but data will not be valid prior to write and will only be held valid after write by the delay to disable the transceiver.

Figure 2C6d. Buffering Devices without OE/RD and with Common or Separate input/Output

One last technique is given for devices with separate inputs and outputs (Fig. 2C6e). Separate bus receivers and drivers are provided rather than a single transceiver. The receiver is always enabled while the bus driver is controlled by  $\overline{\text{RD}}$  and chip select. The only possibility for bus contention in this system occurs as multiple devices on each line of the local read bus are enabled and disabled during chip selection changes.

Throughout this note, the multiplexed bus will be considered the local CPU bus and the demultiplexed address and buffered data bus will be the system bus. For additional information on bus contention and the system problems associated with it, refer to Appendix 1.

Figure 2C6e. Buffering Devices without OE/RD and with Separate Input/Output

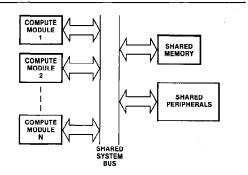

#### 2D. Multiprocessor Environment

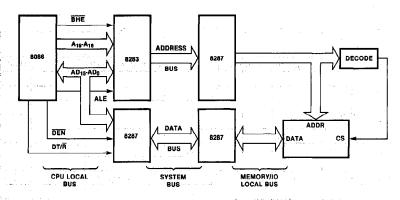

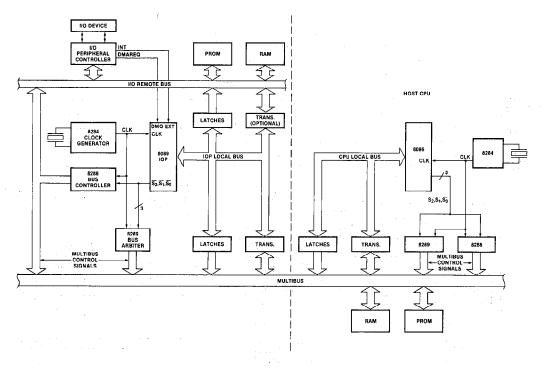

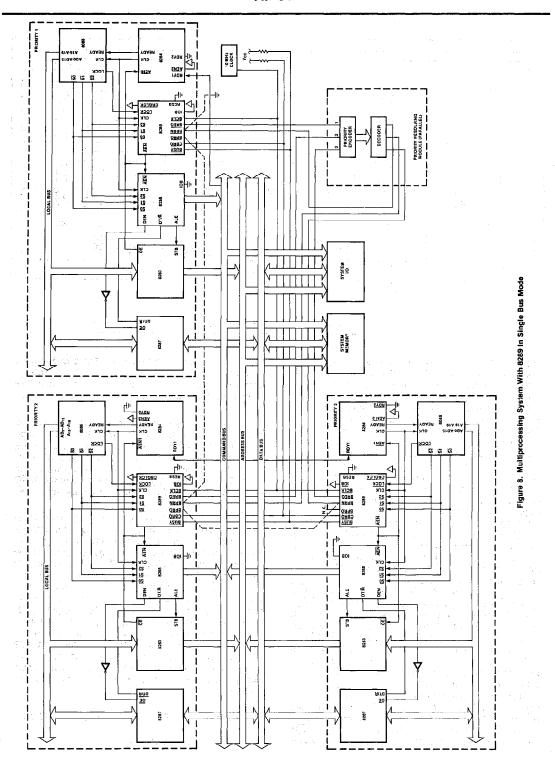

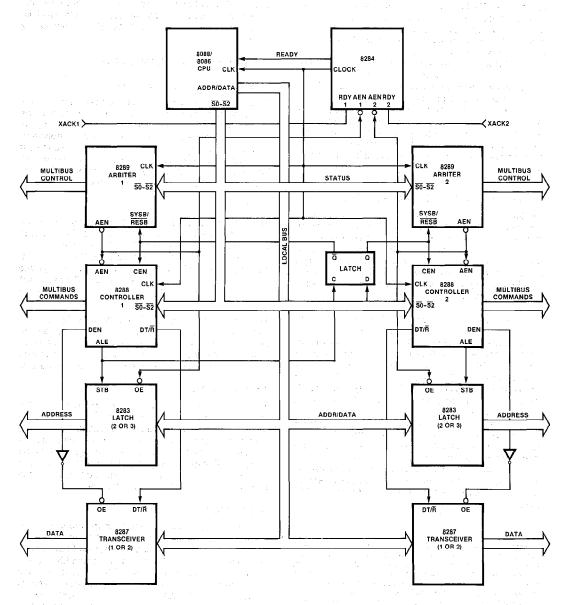

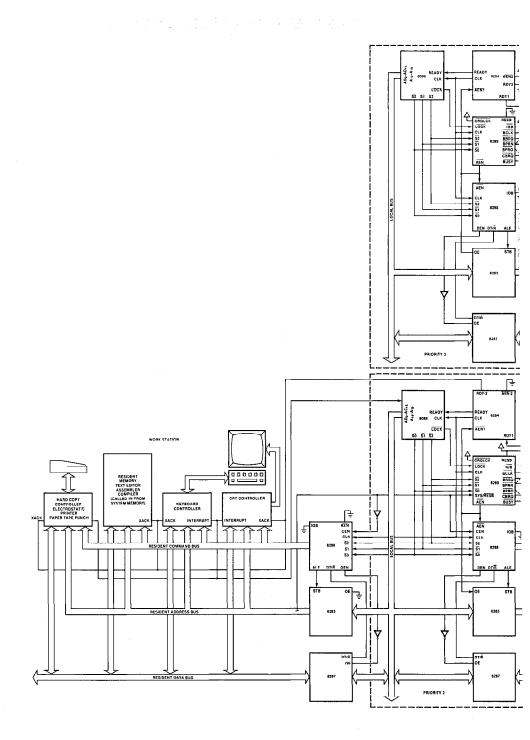

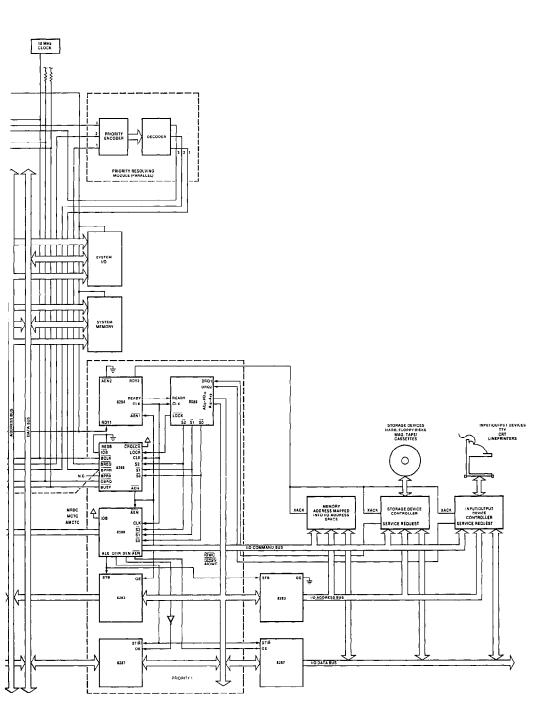

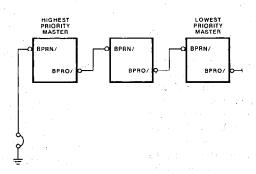

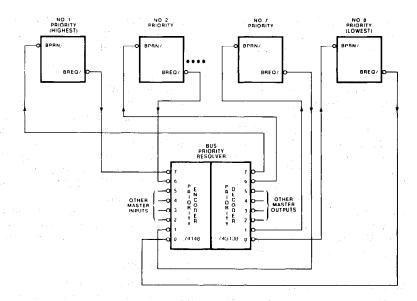

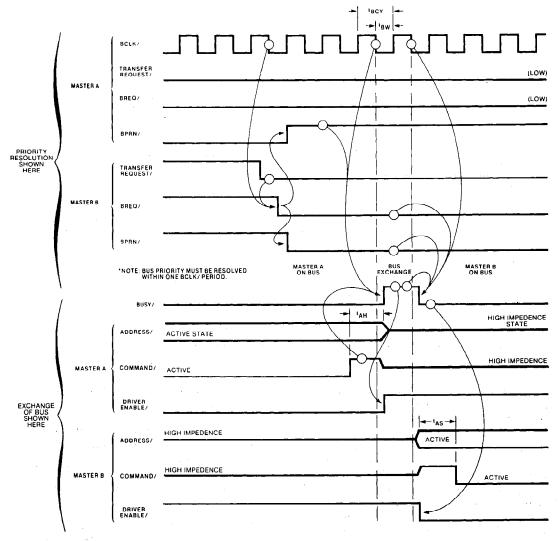

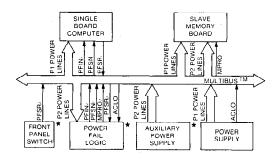

The 8086 architecture supports multiprocessor systems based on the concept of a shared system bus (Fig. 2D1). All CPU's in the system communicate with each other and share resources via the system bus. The bus may be either the Intel Multibus<sup>TM</sup> system bus or an extension of the system bus defined in the previous section. The major addition required to the demultiplexed system bus is arbitration logic to control access to the system bus. As each CPU asynchronously requests access to the shared bus, the arbitration logic resolves priorities and grants bus access to the highest priority CPU. Having gained access to the bus, the CPU completes its transfer and will either relinquish the bus or wait to be forced to relinquish the bus. For a discussion on Multibus<sup>TM</sup> arbitration techniques, refer to AP-28A, Intel Multibus<sup>TM</sup> Interfacing.

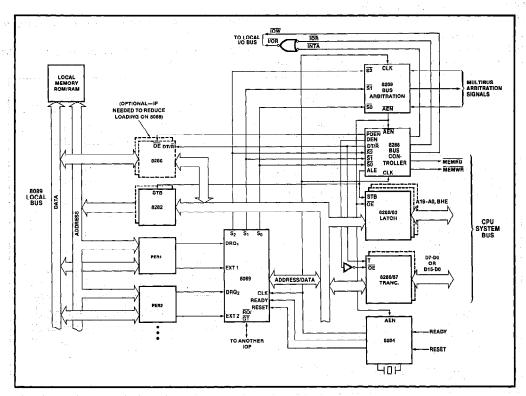

Figure 2D1. 8086 Family Multiprocessor System

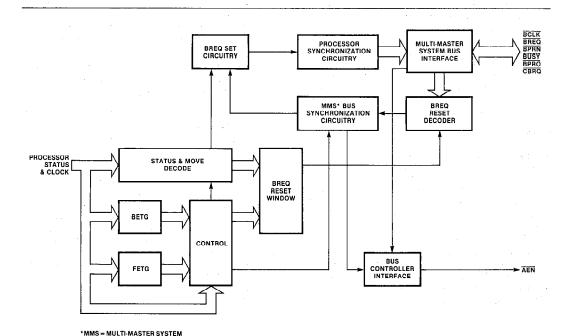

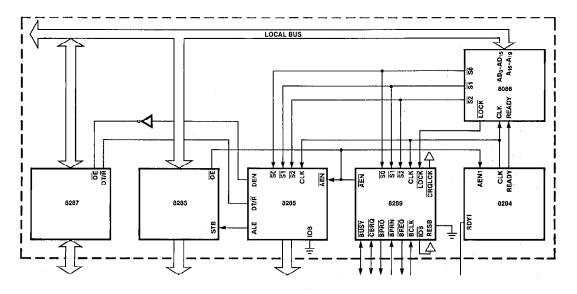

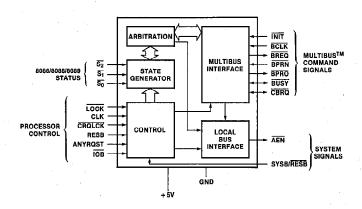

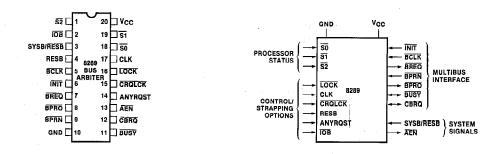

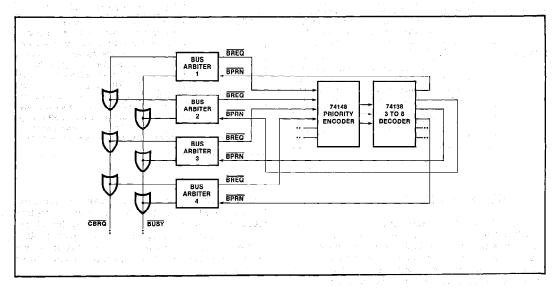

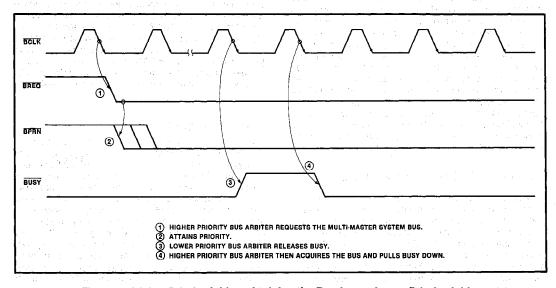

To support a multimaster interface to the Multibus system bus for the 8086 family, the 8289 bus arbiter is included as part of the family. The 8289 is compatible with the 8086's local bus and in conjunction with the 8288 bus controller, implements the Multibus protocol for bus arbitration. The 8289 provides a variety of arbitration and prioritization techniques to allow optimization of bus availability, throughput and utilization of shared resources. Additional features (implemented through

strapping options) extend the configuration options beyond a pure CPU interface to the multimaster system bus for access to shared resources to include concurrent support of a local CPU bus for private resources. For specific configurations and additional information on the 8289, refer to application note AP-51.

#### 3. 8086 SYSTEM DETAILS

#### 3A. Operating Modes

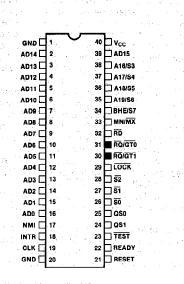

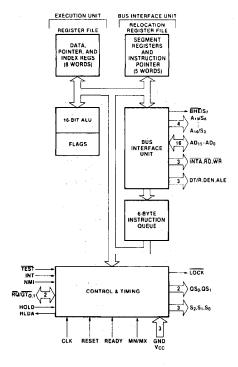

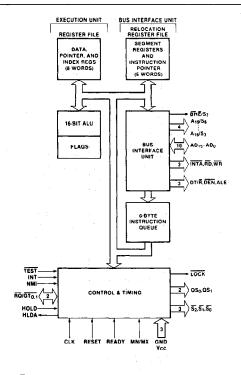

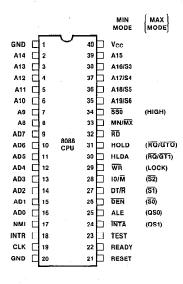

Possibly the most unique feature of the 8086 is the ability to select the base machine configuration most suited to the application. The MN/MX input to the 8086 is a strapping option which allows the designer to select between two functional definitions of a subset of the 8086 outputs.

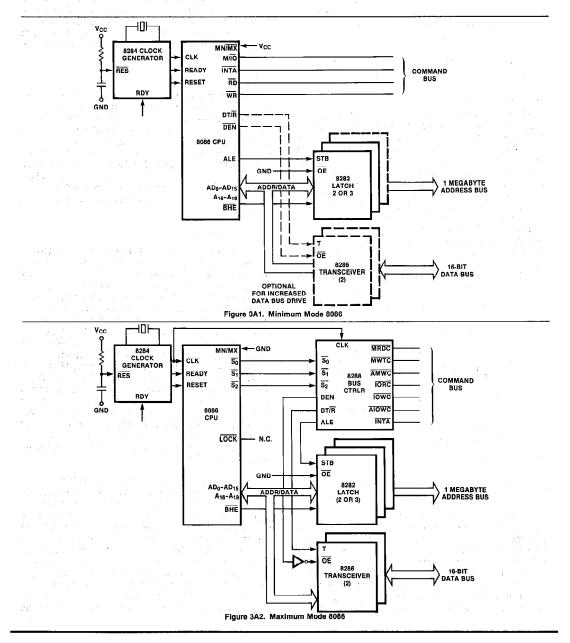

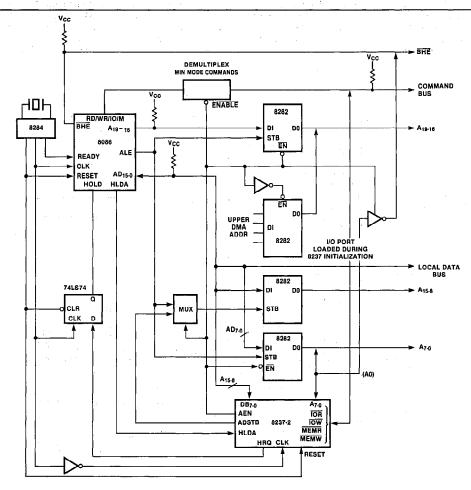

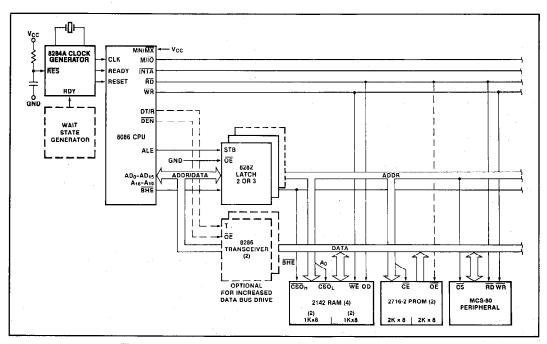

#### MINIMUM MODE

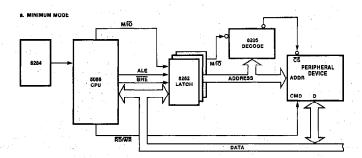

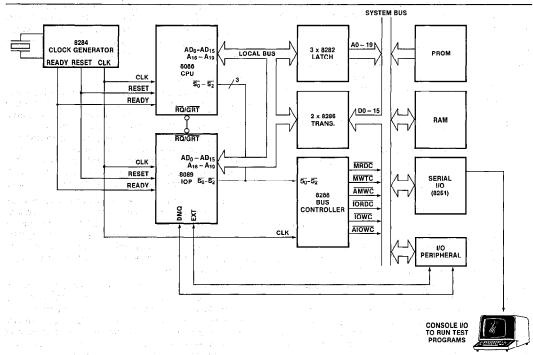

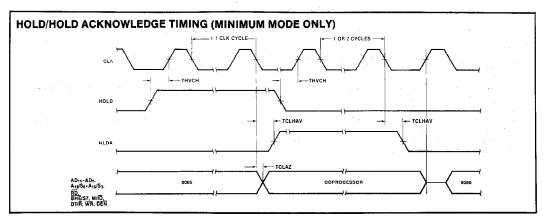

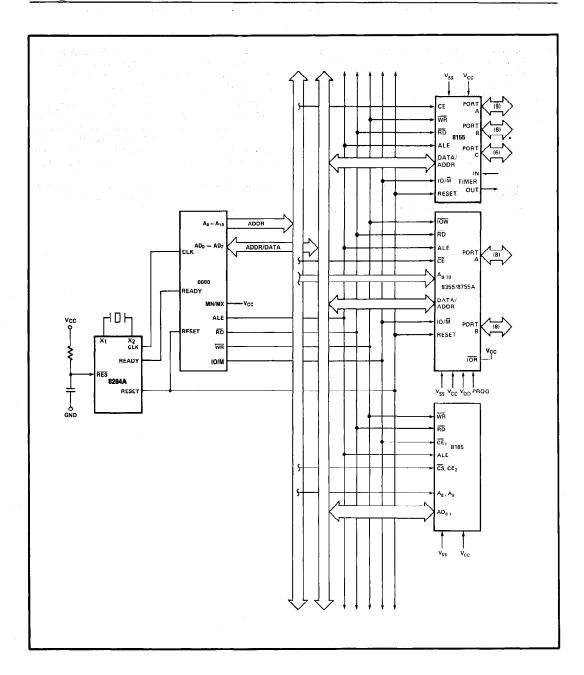

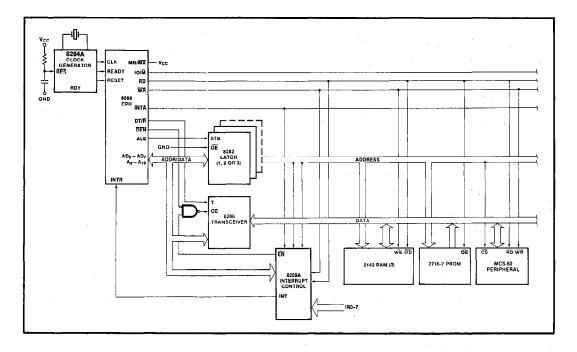

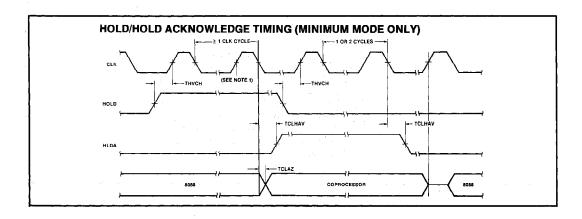

The minimum mode 8086 (Fig. 3A1) is optimized for small to medium (one or two boards), single CPU systems. Its system architecture is directed at satisfying the requirements of the lower to middle segment of high performance 16-bit applications. The CPU maintains the full megabyte memory space, 64K byte I/O space and 16-bit data path. The CPU directly provides all bus control (DT/R, DEN, ALE, M/IO), commands (RD,WR,INTA) and a simple CPU preemption mechanism (HOLD, HLDA) compatible with existing DMA controllers.

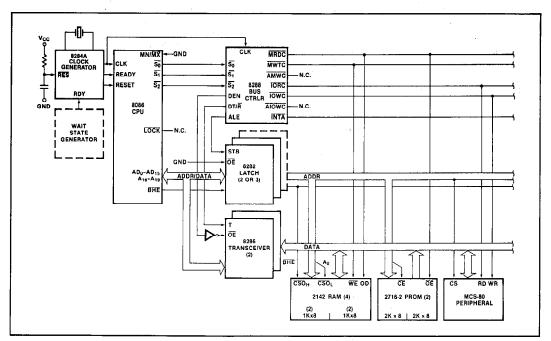

#### MAXIMUM MODE

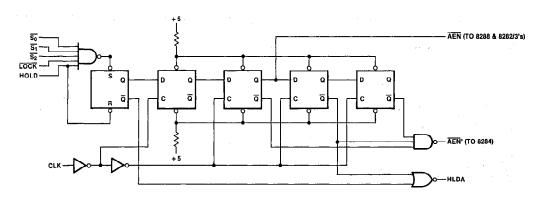

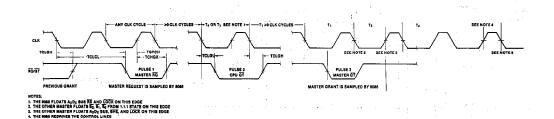

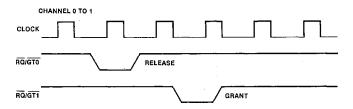

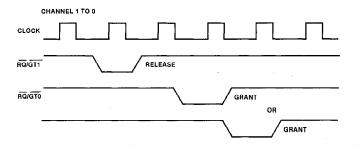

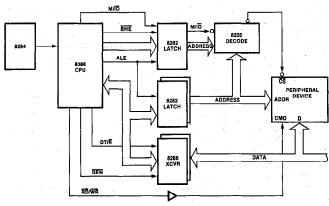

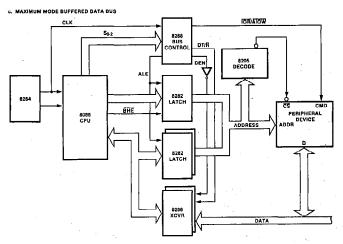

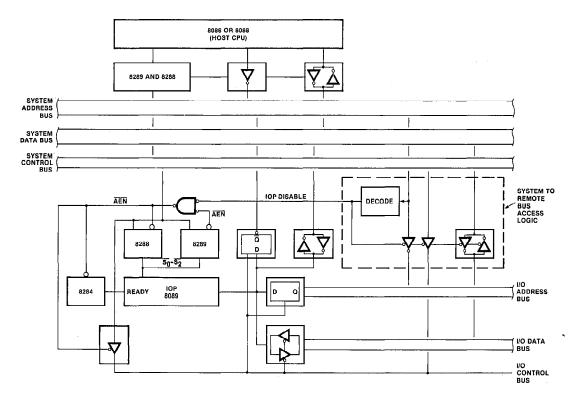

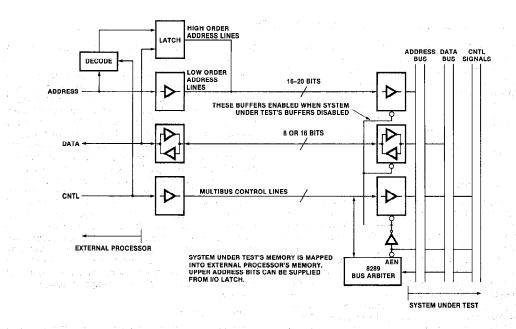

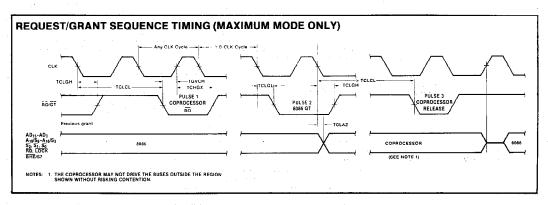

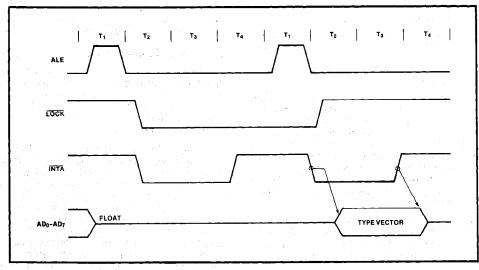

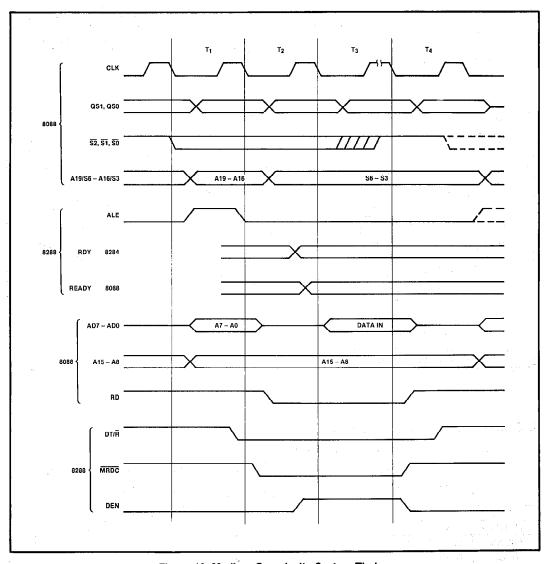

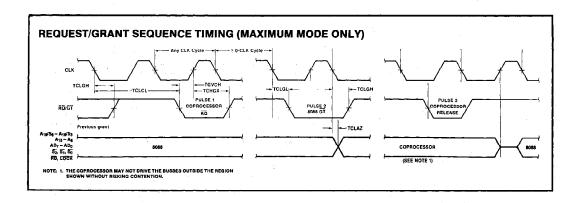

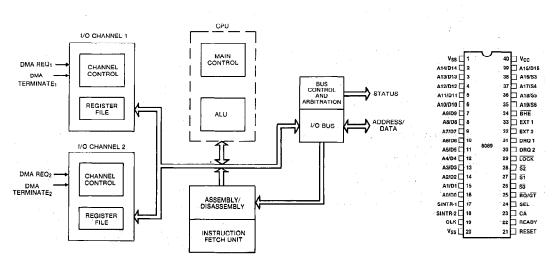

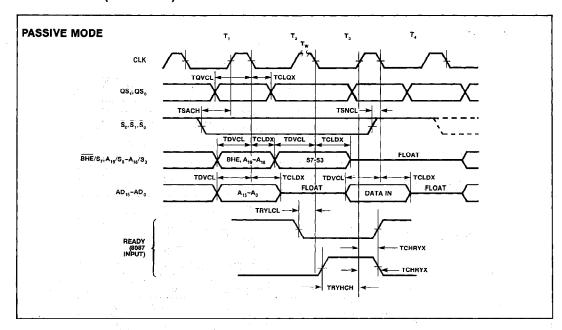

The maximum mode (Fig. 3A2) extends the system architecture to support multiprocessor configurations. and local instruction set extension processors (coprocessors). Through addition of the 8288 bipolar bus controller, the 8086 outputs assigned to bus control and commands in the minimum mode are redefined to allow these extensions and enhance general system performance. Specifically, (1) two prioritized levels of processor preemption (RQ/GT0, RQ/GT1) allow multiple processors to reside on the 8086's local bus and share its interface to the system bus, (2) Queue status (QS0,QS1) is available to allow external devices like ICETM-86 or special instruction set extension co-processors to track the CPU instruction execution, (3) access control to shared resources in multiprocessor systems is supported by a hardware bus lock mechanism and (4) system command and configuration options are expanded via ancillary devices like the 8288 bus controller and 8289 bus arbiter.

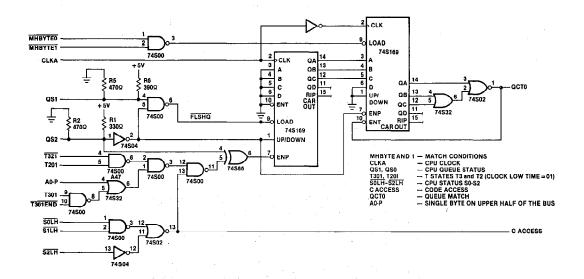

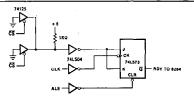

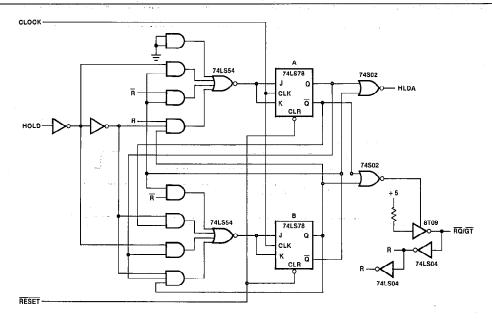

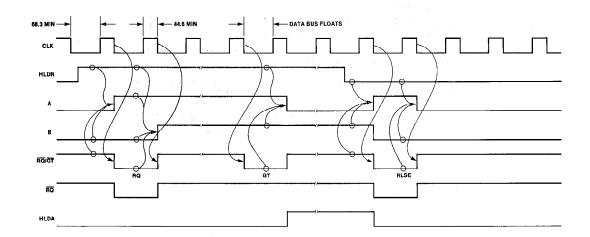

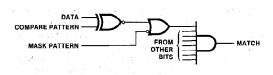

The queue status indicates what information is being removed from the internal queue and when the queue is being reset due to a transfer of control (Table 3A1). By monitoring the  $\overline{50},\overline{51},\overline{52}$  status lines for instructions entering the 8086 (1,0,0 indicates code access while A0 and  $\overline{BHE}$  Indicate word or byte) and QS0, QS1 for instructions leaving the 8086's internal queue, it is possible to track the instruction execution. Since instructions are executed from the 8086's internal queue, the queue status is presented each CPU clock cycle and is not related to the bus cycle activity. This mechanism (1) allows a co-processor to detect execution of an

ESCAPE instruction which directs the co-processor to perform a specific task and (2) allows ICE-86 to trap execution of a specific memory location. An example of a circuit used by ICE is given in Figure 3A3. The first up down counter tracks the depth of the queue while the second captures the queue depth on a match. The second counter decrements on further fetches from the queue until the queue is flushed or the count goes to zero indicating execution of the match address. The first counter decrements on fetch from the queue (QS0=1) and increments on code fetches into the

queue. Note that a normal code fetch will transfer two bytes into the queue so two clock increments are given to the counter (T201 and T301) unless a single byte is loaded over the upper half of the bus (A0-P is high). Since the execution unit (EU) is not synchronized to the bus interface unit (BIU), a fetch from the queue can occur simultaneously with a transfer into the queue. The exclusive-or gate driving the ENP input of the first counter allows these simultaneous operations to cancel each other and not modify the queue depth.

TABLE 3A1. QUEUE STATUS

| QS <sub>1</sub> | QS <sub>0</sub> |                                  |

|-----------------|-----------------|----------------------------------|

| 0 (LOW)         | 0               | No Operation                     |

| 0               | 1               | First Byte of Op Code from Queue |

| 1 (HIGH)        | 0               | Empty the Queue                  |

| 1               | 1               | Subsequent Byte from Queue       |

The queue status is valid during the CLK cycle after which the queue operation is performed.

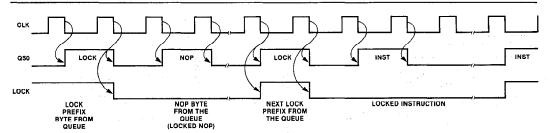

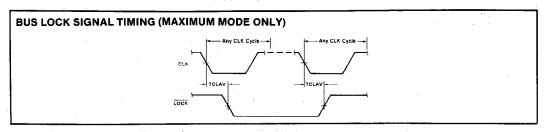

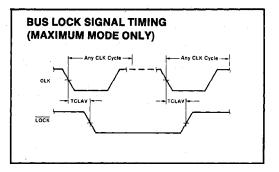

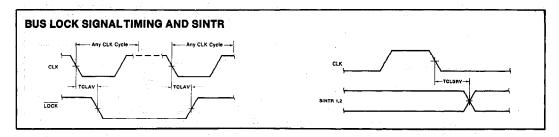

To address the problem of controlling access to shared resources, the maximum mode 8086 provides a hardware LOCK output. The LOCK output is activated through the instruction stream by execution of the LOCK prefix Instruction. The LOCK output goes active in the first CPU clock cycle following execution of the prefix and remains active until the clock following the completion of the instruction following the LOCK prefix. To provide bus access control in multiprocessor systems, the LOCK signal should be incorporated into the system bus arbitration logic resident to the CPU.

During normal multiprocessor system operation, priority of the shared system bus is determined by the arbitration circuitry on a cycle by cycle basis. As each CPU requires a transfer over the system bus, it requests access to the bus via its resident bus arbitration logic. When the CPU gains priority (determined by the system bus arbitration scheme and any associated logic), it takes control of the bus, performs its bus cycle and either maintains bus control, voluntarily releases the bus or is forced off the bus by the loss of priority. The lock mechanism prevents the CPU from losing bus control (either voluntarily or by force) and guarantees a CPU the ability to execute multiple bus cycles (during execu-

tion of the locked instruction) without intervention and possible corruption of the data by another CPU. A classic use of the mechanism is the 'TEST and SET semaphore' during which a CPU must read from a shared memory location and return data to the location without allowing another CPU to reference the same location between the TEST operation (read) and the SET operation (write). In the 8086 this is accomplished with a locked exchange instruction.

LOCK XCHG reg, MEMORY; reg is any register :MEMORY is the address of the ;semaphore

The activity of the LOCK output is shown in Diagram 3A1. Another interesting use of the LOCK for multiprocessor systems is a locked block move which allows high speed message transfer from one CPU's message buffer to another.

During the locked instruction, a request for processor preemption (RQ/GT) is recorded but not acknowledged until completion of the locked instruction. The LOCK has no direct affect on interrupts. As an example, a locked HALT instruction will cause HOLD (or RQ/GT) requests to be ignored but will allow the CPU to exit the HALT state on an interrupt. In general, prefix bytes are considered extensions of the instructions they precede. Therefore, interrupts that occur during execution of a prefix are not acknowledged (assuming interrupts are enabled) until completion of the instruction following the prefixes (except for instructions which allow servicing interrupts during their execution, i.e., HALT, WAIT and repeated string primitives). Note that multiple prefix bytes may precede an instruction. As another example, consider a 'string primitive' preceded by the repetition

Figure 3A3. Example Circuit to Track the 8086 Queue

prefix (REP) which is interruptible after each execution of the string primitive. This holds even if the REP prefix is combined with the LOCK prefix and prevents interrupts from being locked out during a block move or other repeated string operation. As long as the operation is not interrupted, LOCK remains active. Further information on the operation of an interrupted string operation with multiple prefixes is presented in the section dealing with the 8086 interrupt structure.

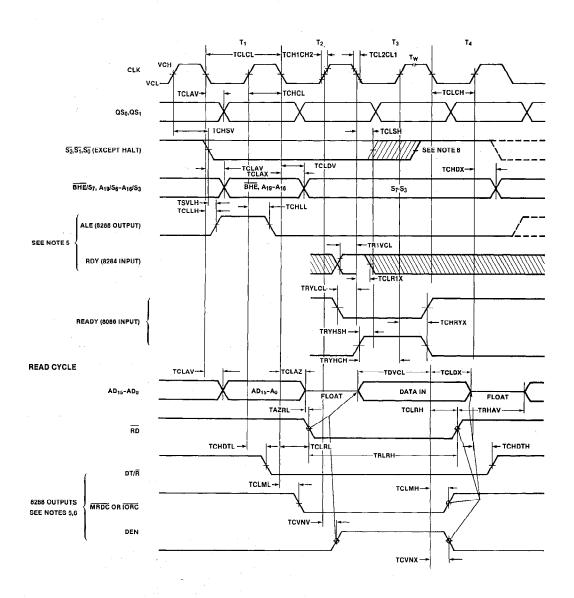

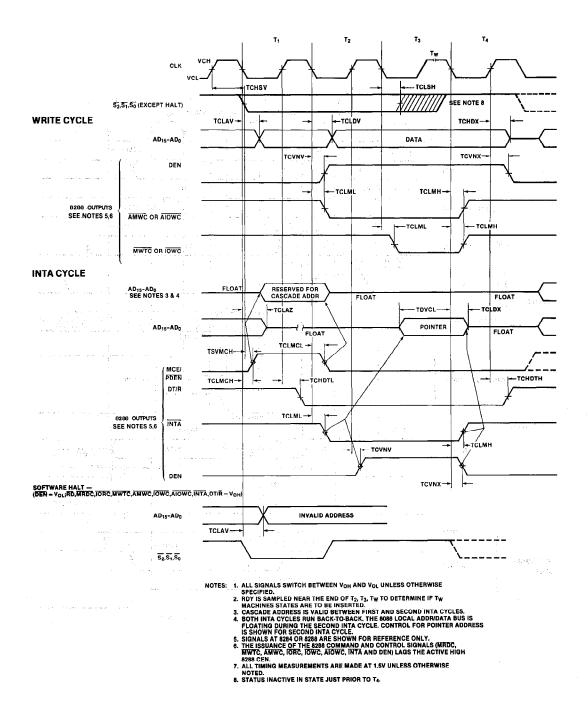

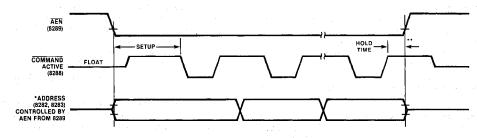

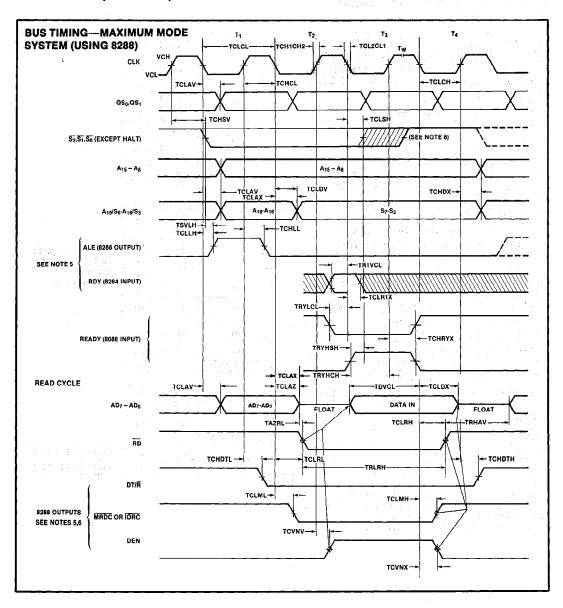

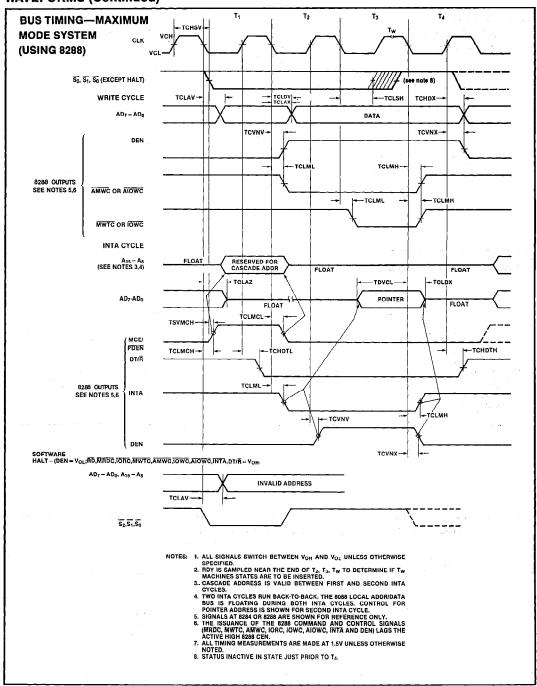

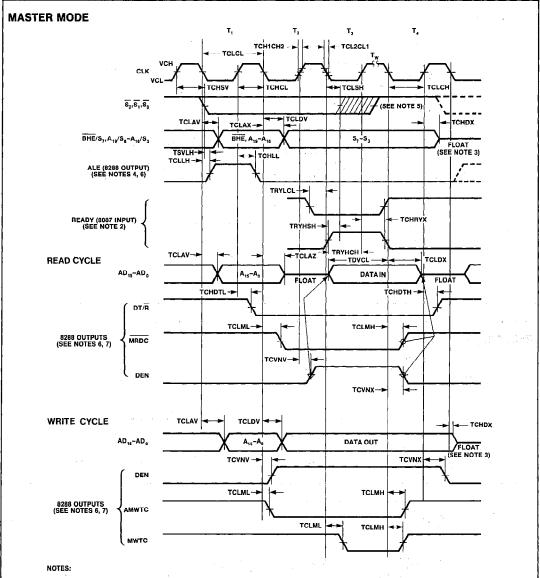

Three additional status lines ( $\overline{S0}$ ,  $\overline{S1}$ ,  $\overline{S2}$ ) are defined to provide communications with the 8288 and 8289. The status lines tell the 8288 when to initiate a bus cycle, what type of command to issue and when to terminate the bus cycle. The 8288 samples the status lines at the beginning of each CPU clock (CLK). To initiate a bus cycle, the CPU drives the status lines from the passive state  $(\overline{S0}, \overline{S1}, \overline{S2} = 1)$  to one of seven possible command codes (Table 3A2). This occurs on the rising edge of the clock during T4 of the previous bus cycle or a TI (idle cycle, no current bus activity). The 8288 detects the status change by sampling the status lines on the high to low transition of each clock cycle. The 8288 starts a bus cycle by generating ALE and appropriate buffer direction control in the clock cycle immediately following detection of the status change (T1). The bus transceivers and the selected command are enabled in the next clock cycle (T2) (or T3 for normal write commands). When the status returns to the passive state, the 8288 will terminate the command as shown in Diagram 3A2. Since the CPU will not return the status to the passive state until the 'ready' indication is received, the 8288 will maintain active command and bus control for any number of wait cycles. The status lines may also be used by other processors on the 8086's local bus to monitor bus activity and control the 8288 if they gain control of the local bus.

TABLE 3A2. STATUS LINE DECODES

| S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> |                       |

|----------------|----------------|----------------|-----------------------|

| 0 (LOW)        | 0              | 0              | Interrupt Acknowledge |

| 0              | 0 -            | 1              | Read I/O Port         |

| 0              | 1              | 0              | Write I/O Port        |

| 0              | 1              | 1 1            | Halt                  |

| 1 (HIGH)       | 0              | 0              | Code Access           |

| 1              | 0              | 1              | Read Memory           |

| 1 1            | 1              | 0              | Write Memory          |

| 1              | 1              | 1              | Passive               |

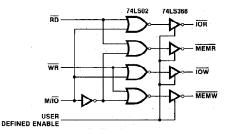

The 8288 provides the bus control (DEN, DT/R, ALE) and commands (INTA, MRDC, IORC, MWTC, AMWC, IOWC, AIOWC) removed from the CPU. The command structure has separate read and write commands for memory and I/O to provide compatibility with the Multibus command structure.

The advanced write commands are enabled one clock period earlier than the normal write to accommodate the wider write pulse widths often required by peripherals and static RAMs. The normal write provides data setup prior to write to accommodate dynamic RAM memories and I/O devices which strobe data on the leading edge of write. The advanced write commands do not guarantee that data is valid prior to the leading edge of the command. The DEN signal in the maximum mode is inverted from the minimum mode to extend transcelver control by allowing logical conjunction of DEN with other signals. While not appearing to be a significant benefit in the basic maximum mode configuration, introduction of interrupt control and various system configurations will demonstrate the usefulness of qualifying DEN. Diagram 3A3 compares the timing of the minimum and maximum mode bus transfer commands. Although the

- 1 QUEUE STATUS INDICATES FIRST BYTE OF OPCODE FROM THE QUEUE.

- 2 THE LOCK OUTPUT WILL GO INACTIVE BETWEEN SEPARATE LOCKED INSTRUCTIONS.

- 3 TWO CLOCKS ARE REQUIRED FOR DECODE OF THE LOCK PREFIX AND ACTIVATION OF THE LOCK SIGNAL.

- 4 SINCE QUEUE STATUS REFLECTS THE QUEUE OPERATION IN THE PREVIOUS CLOCK CYCLE, THE LOCK OUTPUT ACTUALLY GOES ACTIVE COINCIDENT WITH THE START OF THE NEXT INSTRUCTION AND REMAINS ACTIVE FOR ONE CLOCK CYCLE FOLLOWING THE INSTRUCTION.

- 5 IF THE INSTRUCTION FOLLOWING THE LOCK PREFIX IS NOT IN THE QUEUE, THE LOCK OUTPUT STILL GOES ACTIVE AS SHOWN WHILE THE INSTRUCTION IS BEING FETCHED.

- 6 THE BIU WILL STILL PERFORM INSTRUCTION FETCH CYCLES DURING EXECUTION OF A LOCKED INSTRUCTION. THE LOCK MERELY LOCKS THE BUS TO THIS CPU FOR WHATEVER BUS CYCLES THE CPU PERFORMS DURING THE LOCKED INSTRUCTION.

Diagram 3A1. 8086 Lock Activity

maximum mode configuration is designed for multiprocessor environments, large single CPU designs (either Multibus systems or greater than two PC boards) should also use the maximum mode. Since the 8288 is a bipolar dedicated controller device, its output drive for the commands (32 mA) and tolerances on AC characteristics (timing parameters and worse case delays) provide better large system performance than the minimum mode 8086.

In addition to assuming the functions removed from the CPU, the 8288 provides additional strapping options and controls to support multiprocessor configurations and peripheral devices on the CPU local bus. These capabilities allow assigning resources (memory or I/O) as shared (available on the Multibus system bus) or private (accessible only by this CPU) to reduce contention for access to the Multibus system bus and improve multi-CPU system performance. Specific configuration possibilities are discussed in AP-51.

#### 3B. Clock Generation

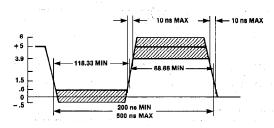

The 8086 requires a clock signal with fast rise and fall times (10 ns max) between low and high voltages of -0.5 to +0.6 low and 3.9 to VCC+1.0 high. The maximum clock frequency of the 8086 is 5 MHz and 8 MHz for the 8086-2. Since the design of the 8086 incorporates dynamic cells, a minimum frequency of 2 MHz is required to retain the state of the machine. Due to the minimum frequency requirement, single stepping or cycling of the CPU may not be accomplished by disabling the clock. The timing and voltage requirements of the CPU clock are shown in Figure 3B1. In general, for frequencies below the maximum, the CPU clock need not satisfy the frequency dependent pulse width limitations stated in the 8086 data sheet. The values specified only reflect the minimum values which must be satisfied and are stated in terms of the maximum clock frequency. As the clock frequency approaches the maximum frequency of the CPU, the clock must conform to a 33% duty cycle to satisfy the CPU minimum clock low and high time specifications.

Flaure 3B1, 8086 Clock

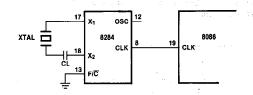

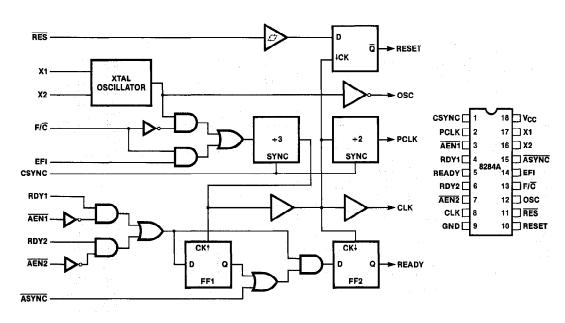

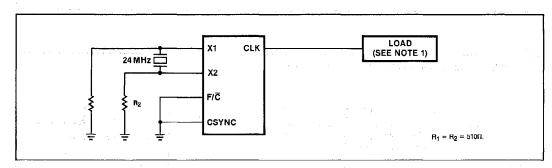

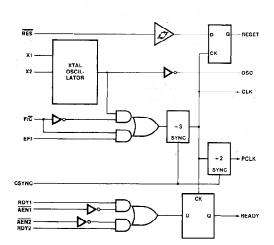

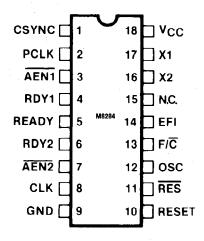

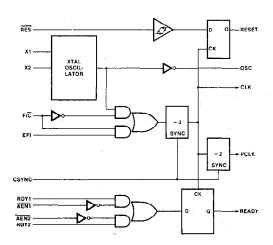

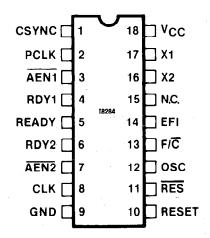

An optimum 33% duty cycle clock with the required voltage levels and transition times can be obtained with the 8284 clock generator (Fig. 3B2). Either an external frequency source or a series resonant crystal may drive the 8284. The selected source must oscillate at 3X the desired CPU frequency. To select the crystal inputs of the 8284 as the frequency source for clock generation, the F/C input to the 8284 must be strapped to ground. The strapping option allows selecting either the crystal or the external frequency input as the source for clock generation. Although the 8284 provides an input for a tank circuit to accommodate overtone mode crystals. fundamental mode crystals are recommended for more accurate and stable frequency generation. When selecting a crystal for use with the 8284, the series resistance should be as low as possible. Since other circuit components will tend to shift the operating frequency from resonance, the operating impedance will typically be higher than the specified series resistance. If the attenuation of the oscillator's feedback circuit reduces the loop gain to less than one, the oscillator will fail. Since the oscillator delays in the 8284 appear as inductive elements to the crystal, causing it to run at a frequency below that of the pure series resonance, a capacitor should be placed in series with the crystal and the X2 input of the 8284. This capacitor serves to cancel this inductive element. The value of the capacitor (CL)

must not cause the impedance of the feedback circuit to reduce the loop gain below one. The impedance of the capacitor is a function of the operating frequency and can be determined from the following equation:

$XCL = 1/2\pi^*F^*CL$

Figure 3B2. 8284 Clock Generator

It is recommended that the crystal series resistance plus XCL be kept less than 1K ohms. This capacitor also serves to debias the crystal and prevent a DC voltage bias from straining and perhaps damaging the crystalline structure. As the crystal frequency increases, the amount of capacitance should be decreased. For example, a 12 MHz crystal may require CL  $\sim$  24 pF while 22 MHz may require CL  $\sim$  8 pF. If very close correlation with the pure series resonance is not necessary, a nominal CL value of 12-15 pF may be used with a 15 MHz crystal (5 MHz 8086 operation). Board layout and component variances will affect the actual amount of inductance and therefore the series capacitance required to cancel it out (this is especially true for wire-wrapped layouts).

Two of the many vendors which supply crystals for Intel microprocessors are listed in Table 3B1 along with a list of crystal part numbers for various frequencies which may be of interest. For additional information on specifying crystals for Intel components refer to application note AP-35.

**TABLE 3B1. CRYSTAL VENDORS**

| f        | Parailei/<br>Series | Crystek <sup>(1)</sup><br>Corp. | CTS Knight, <sup>(2)</sup><br>Inc. |

|----------|---------------------|---------------------------------|------------------------------------|

| 15.0 MHz | S                   | CY15A                           | MP150                              |

| 18.432   | s                   | CY19B*                          | MP184*                             |

| 24.0 MHz | S                   | CY24A                           | MP240                              |

\*Intel also supplies a crystal numbered 8801 for this application.

Notes: 1. Address: 1000 Crystal Drive, Fort Meyers, Florida 33901

2. Address: 400 Reimann Ave., Sandwich, Illinois

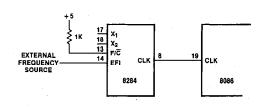

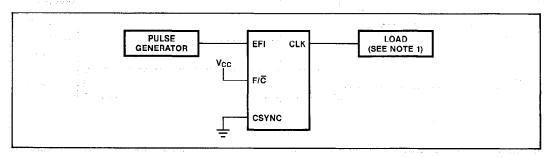

If a high accuracy frequency source, externally variable frequency source or a common source for driving multiple 8284's is desired, the External Frequency Input (EFI) of the 8284 can be selected by strapping the F/C input to 5 volts through ~1K ohms (Fig. 3B3). The external frequency source should be TTL compatible, have a 50% duty cycle and oscillate at three times the desired CPU operating frequency. The maximum EFI frequency the 8284 can accept is slightly above 24 MHz with minimum clock low and high times of 13 ns. Although

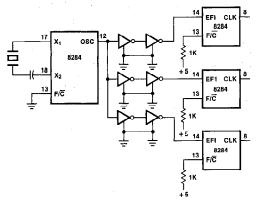

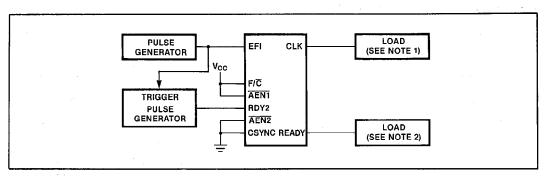

no minimum EFI frequency is specified, it should not violate the CPU minimum clock rate. If a common frequency source is used to drive multiple 8284's distributed throughout the system, each 8284 should be driven by its own line from the source. To minimize noise in the system, each line should be a twisted pair driven by a buffer like the 74LS04 with the ground of the twisted pair connecting the grounds of the source and receiver. To minimize clock skew, the lines to all 8284's should be of equal length. A simple technique for generating a master frequency source for additional 8284's is shown in Figure 3B4. One 8284 with a crystal is used to generate the desired frequency. The oscillator output of the 8284 (OSC) equals the crystal frequency and is used to drive the external frequency to all other 8284's in the system.

Figure 3B3. 8284 with External Frequency Source

Figure 3B4. External Frequency for Multiple 8284s

The oscillator output is inverted from the oscillator signal used to drive the CPU clock generator circuit. Therefore, the oscillator output of one 8284 should not drive the EFI input of a second 8284 if both are driving clock inputs of separate CPU's that are to be synchronized. The variation on EFI to CLK delay over a range of 8284's may approach 35 to 45 ns. If, however, all 8284's are of the same package type, have the same relative supply voltage and operate in the same temperature environment, the variation will be reduced to between 15 and 25 ns.

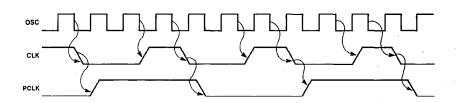

There are three frequency outputs from the 8284, the oscillator (OSC) mentioned above, the system clock (CLK) which drives the CPU, and a peripheral clock (PCLK) that runs at one half the CPU clock frequency. The oscillator output is only driven by the crystal and is not affected by the F/C strapping option. If a crystal is not connected to the 8284 when the external frequency input is used, the oscillator output is indeterminate. The CPU clock is derived from the selected frequency source by an internal divide by three counter. The counter generates the 33% duty cycle clock which is optimum for the CPU at maximum frequency. The peripheral clock has a 50% duty cycle and is derived from the CPU clock. Diagram 3B0 shows the relationship of CLK to OSC and PCLK to CLK. The maximum skew is 20 ns between OSC and CLK, and 22 ns between CLK and PCLK.

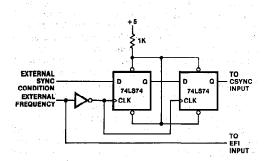

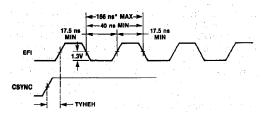

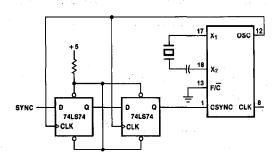

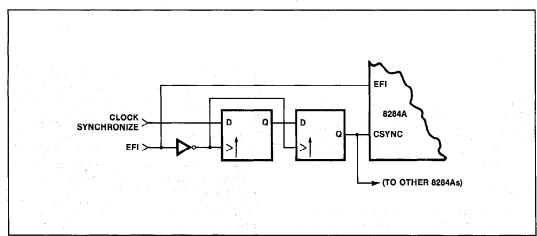

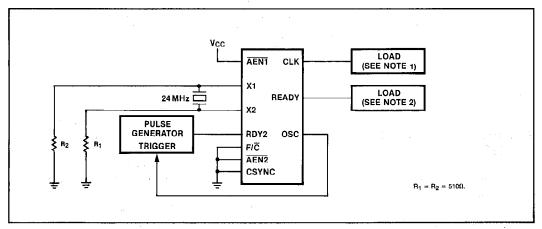

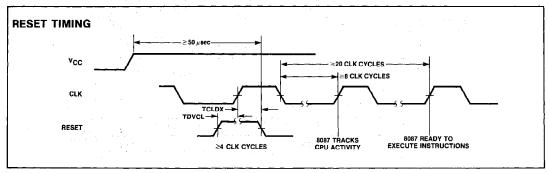

Since the state of the 8284 divide by three counter is indeterminate at system initialization (power on), an external sync to the counter (CSYNC) is provided to allow synchronization of the CPU clock to an external event. When CSYNC is brought high, the CLK and PCLK outputs are forced high. When CSYNC returns low, the next positive clock from the frequency source starts clock generation. CSYNC must be active for a minimum of two periods of the frequency source. If CSYNC is asynchronous to the frequency source, the circuit in Figure 3B5 should be used for synchronization. The two latches minimize the probability of a meta-stable state in the latch driving CSYNC. The latches are clocked with the inverse of the frequency source to guarantee the 8284 setup and hold time of CSYNC to the frequency source (Diag. 3B1). If a single 8284 is to be synchronized to an external event and an external frequency source is not used, the oscillator output of the 8284 may be used to

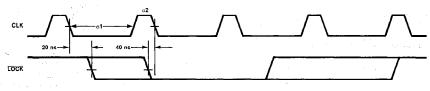

Diagram 3B0. OSC → CLK and CLK → PCLK Relationships

synchronize CSYNC (Fig. 3B6). Since the oscillator output is inverted from the internal oscillator signal, the inverter in the previous example is not required. If multiple 8284's are to be synchronized, an external frequency source must drive all 8284's and a single CSYNC synchronization circuit must drive the CSYNC input of all 8284's (Fig. 3B7). Since activation of CSYNC may cause violation of CPU minimum clock low time, it should only be enabled during reset or CPU clock high. CSYNC must also be disabled a minimum of four CPU clocks before the end of reset to guarantee proper CPU reset.

Figure 3B5. Synchronizing CSYNC with EFI

\*MAX IS SPEC'ED TO GUARANTEE MAX 8086 CLOCK FREQUENCY

Diagram 3B1. CSYNC Setup and Hold to EFI

Figure 3B6. EFI from 8284 Oscillator

Figure 3B7. Synchronizing Multiple 8284s

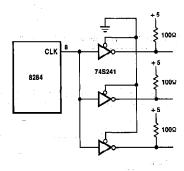

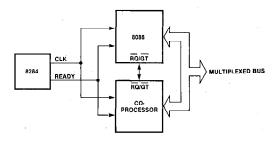

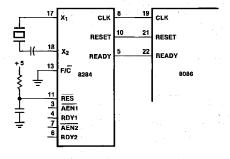

Due to the fast transitions and high drive (5 mA) of the 8284 CLK output, it may be necessary to put a 10 to 100 ohm resistor in series with the clock line to eliminate ringing (resistor value depending on the amount of drive required). If multiple sources of CLK are needed with minimum skew, CLK can be buffered by a high drive device (74S241) with outputs tied to 5 volts through 100 ohms to guarantee VOH = 3.9 min (8086 minimum clock input high voltage) (Fig. 3B8). A single 8284 should not be used to generate the CLK for multiple CPU's that do not share a common local (multiplexed) bus since the 8284 synchronizes ready to the CPU and can only accommodate ready for a single CPU. If multiple CPU's share a local bus, they should be driven with the same clock to optimize transfer of bus control. Under these circumstances, only one CPU will be using the bus for a particular bus cycle which allows sharing a common READY signal (Fig. 3B9).

Figure 3B8. Buffering the 8284 CLK Output

Figure 3B9. 8086 and Co-Processor on the Local Bus Share a Common 8284

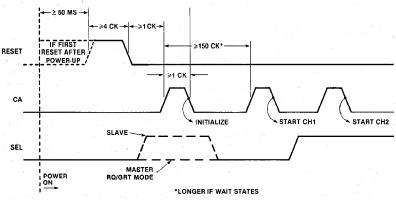

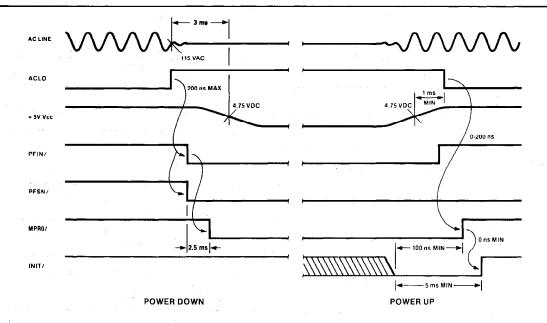

#### 3C. Reset

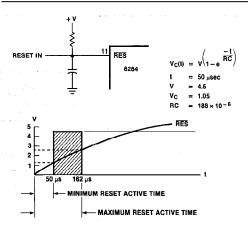

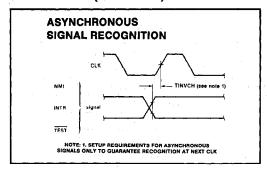

The 8086 requires a high active reset with minimum pulse width of four CPU clocks except after power on which requires a 50  $\mu s$  reset pulse. Since the CPU internally synchronizes reset with the clock, the reset is internally active for up to one clock period after the external reset. Non-Maskable Interrupts (NMI) or hold requests on  $\overline{RQ/GT}$  which occur during the internal reset, are not acknowledged. A minimum mode hold request or maximum mode  $\overline{RQ}$  pulses active immediately after the internal reset will be honored before the first instruction fetch.

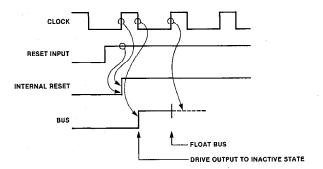

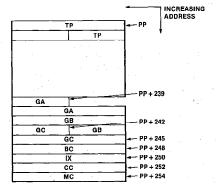

From reset, the 8086 will condition the bus as shown in Table 3C1. The multiplexed bus will three-state upon detection of reset by the CPU. Other signals which three-state will be driven to the inactive state for one clock low interval prior to entering three-state (Fig. 3C1). In the minimum mode, ALE and HLDA are driven inactive and are not three-stated. In the maximum mode,  $\overline{\text{RO}/\text{GT}}$  lines are held inactive and the queue status indicates no activity. The queue status will not indicate a reset of the queue so any user defined external circuits monitoring the queue should also be reset by the system reset. 22K ohm pull-up resistors should be connected to the CPU command and bus control lines to

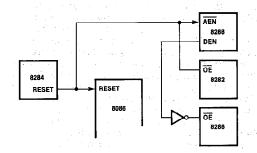

quarantee the inactive state of these lines in systems where leakage currents or bus capacitance may cause the voltage levels to settle below the minimum high voltage of devices in the system. In maximum mode systems, the 8288 contains internal pull-ups on the \$0.52 inputs to maintain the inactive state for these lines when the CPU floats the bus. The high state of the status lines during reset causes the 8288 to treat the reset sequence as a passive state. The condition of the 8288 outputs for the passive state are shown in Table 3C2. If the reset occurs during a bus cycle, the return of the status lines to the passive state will terminate the bus cycle and return the command lines to the inactive state. Note that the 8288 does not three-state the command outputs based on the passive state of the status lines. If the designer needs to three-state the CPU off the bus during reset in a single CPU system, the reset signal should also be connected to the 8288's AEN input and the output enable of the address latches (Fig. 3C2). This forces the command and address bus interface to three-state while the inactive state of DEN from the 8288 three-states the transceivers on the data bus.

Table 3C1. 8086 Bus During Reset

| Signals                              | Condition                      |

|--------------------------------------|--------------------------------|

| AD <sub>15-0</sub>                   | Three-State                    |

| A <sub>19-16</sub> /S <sub>6-3</sub> | Three-State                    |

| BHE/S <sub>7</sub>                   | Three-State                    |

| \$2/(M/10)                           | Driven to "1" then three-state |

| \$1/(DT/R)                           | Driven to "1" then three-state |

| S0/DEN                               | Driven to "1" then three-state |

| LOCK/WR                              | Driven to "1" then three-state |

| RD_                                  | Driven to "1" then three-state |

| INTÄ                                 | Driven to "1" then three-state |

| ALE                                  | 0                              |

| HLDA                                 | 0 .                            |

| RQ/GT0                               | 1                              |

| RQ/GT1                               | . 1                            |

| QS0                                  | 0                              |

| QS1                                  | 0                              |

Figure 3C1. 8086 Bus Conditioning on Reset

TABLE 3C2. 8288 OUTPUTS DURING PASSIVE MODE

| ALE      | 0   |

|----------|-----|

| DEN      | 0   |

| DT/R     | 1   |

| MCE/PDEN | 0/1 |

| COMMANDS | 1   |

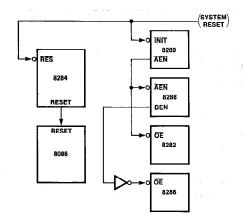

Figure 3C2. Reset Disable for Max Mode 8086 Bus Interface

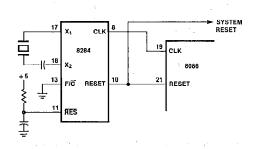

For multiple processor systems using arbitration of a multimaster bus, the system reset should be connected to the INIT input of the 8289 bus arbiter in addition to the 8284 reset input (Fig. 3C3). The low active INIT input forces all 8289 outputs to their inactive state. The inactive state of the 8289 ĀEN output will force the 8288 to three-state the command outputs and the address latches to three-state the address bus interface. DEN inactive from the 8288 will three-state the data bus interface. For the multimaster CPU configuration, the reset should be common to all CPU's (8289's and 8284's) and satisfy the maximum of either the CPU reset requirements or 3 TBLBL (3 8289 bus clock times)+3 TCLCL (3 8086 clock cycle times) to satisfy 8289 reset requirements.

Figure 3C3. Reset Disable of for Max Mode 8086 Bus Interface in Multi CPU System

If the 8288 command outputs are three-stated during reset, the command lines should be pulled up to  $V_{CC}$  through 2.2K ohm resistors.

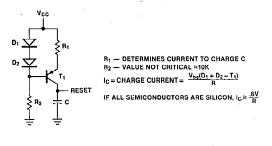

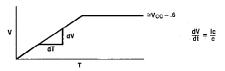

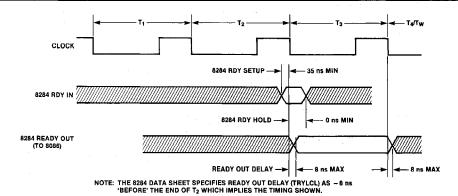

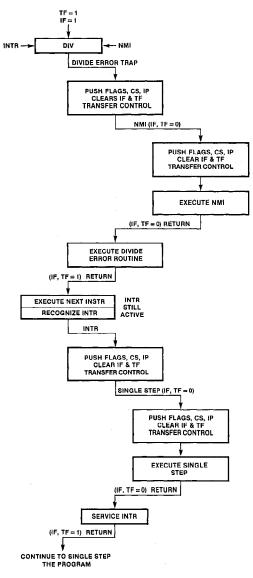

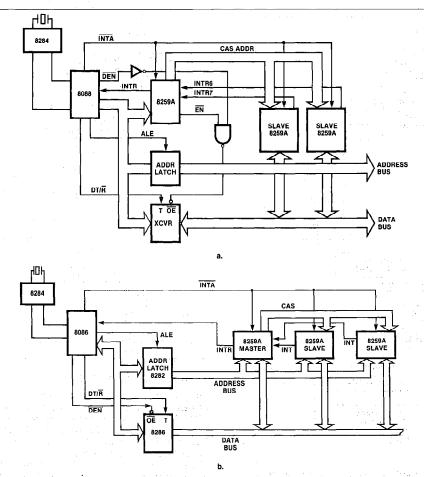

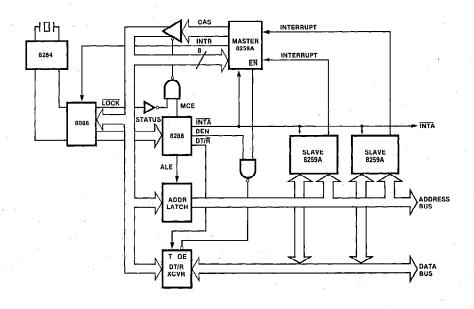

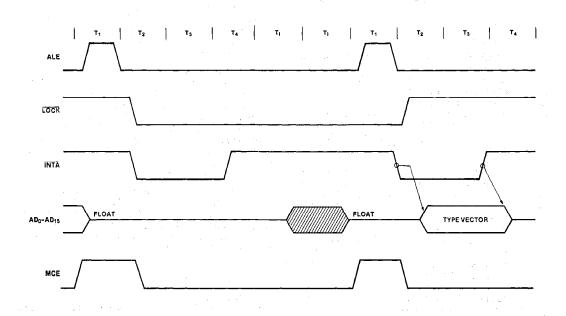

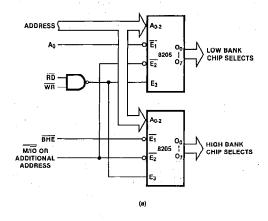

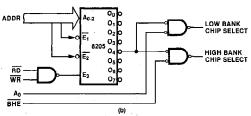

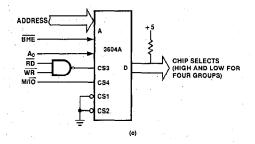

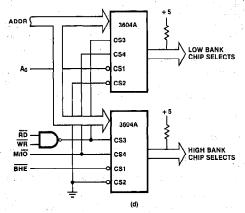

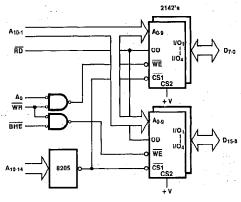

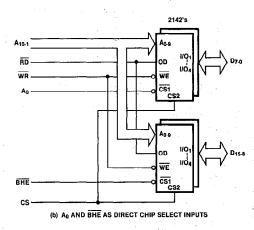

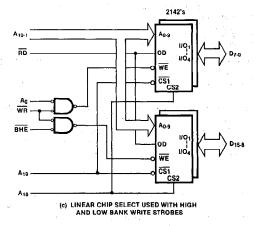

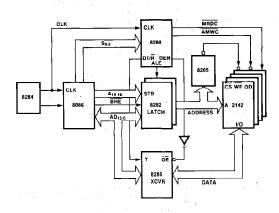

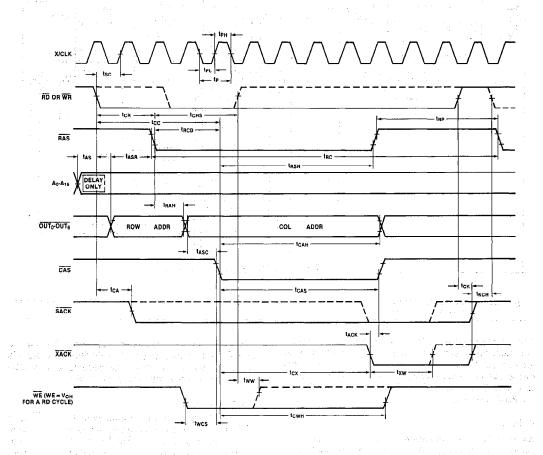

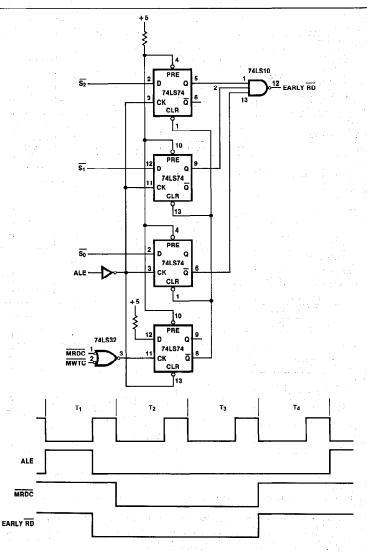

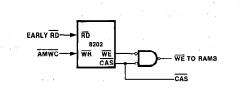

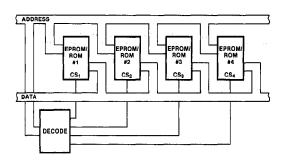

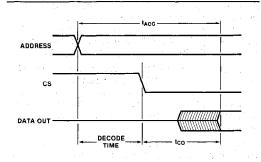

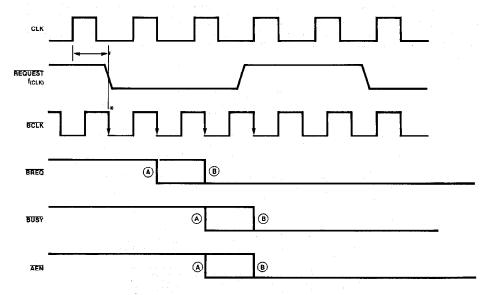

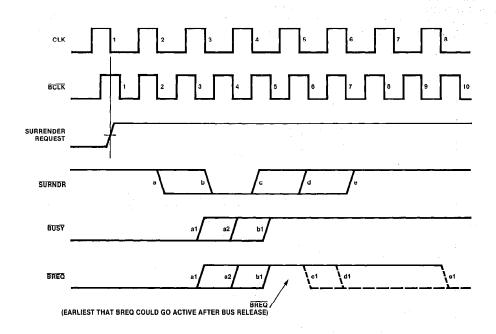

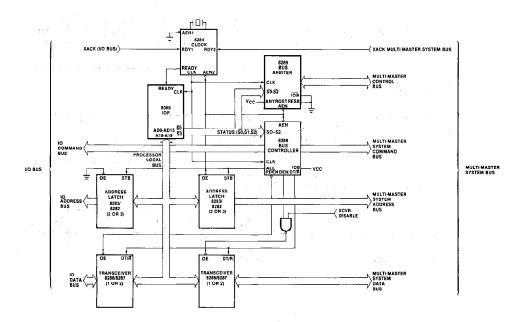

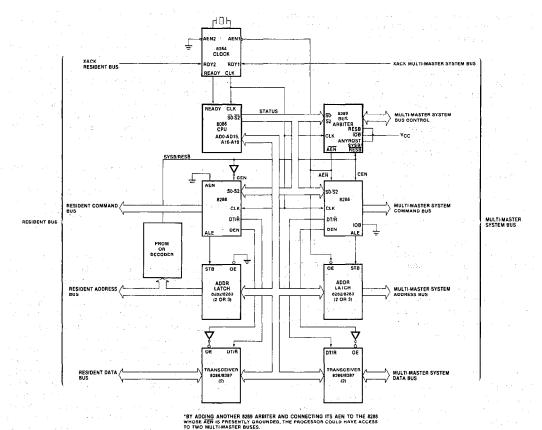

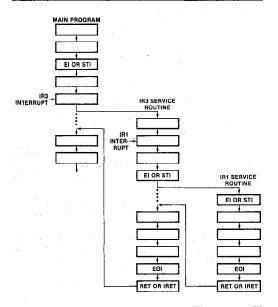

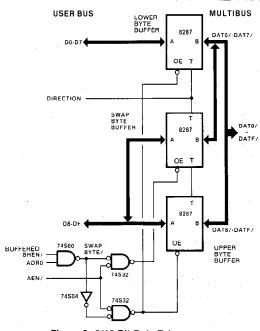

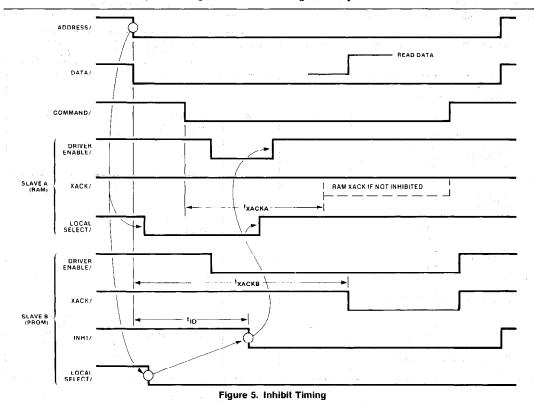

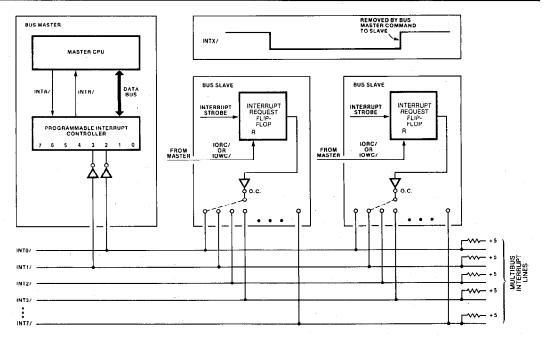

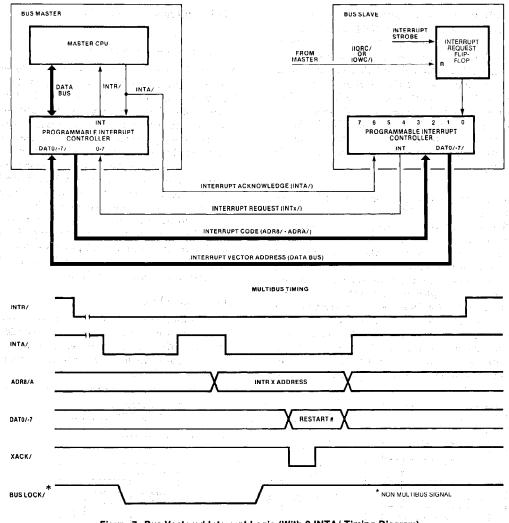

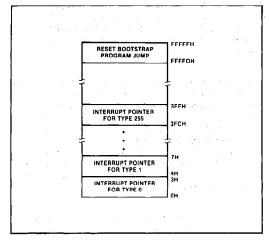

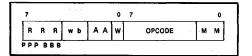

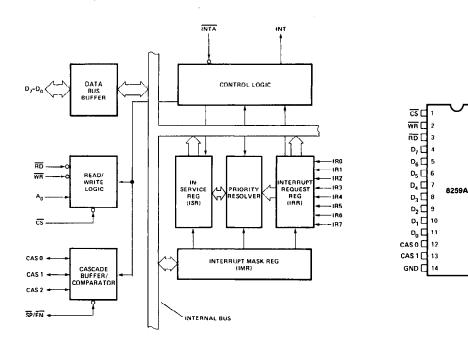

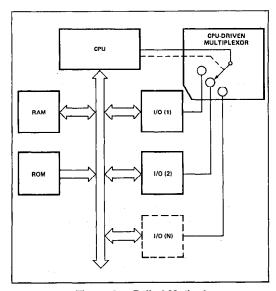

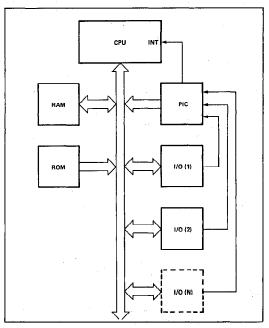

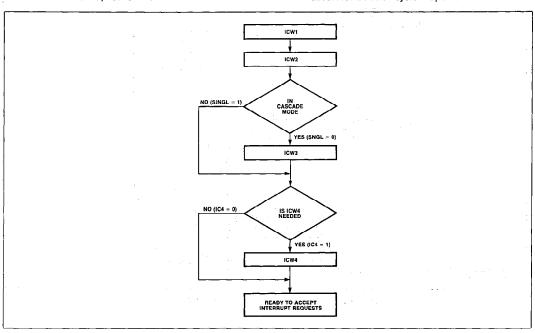

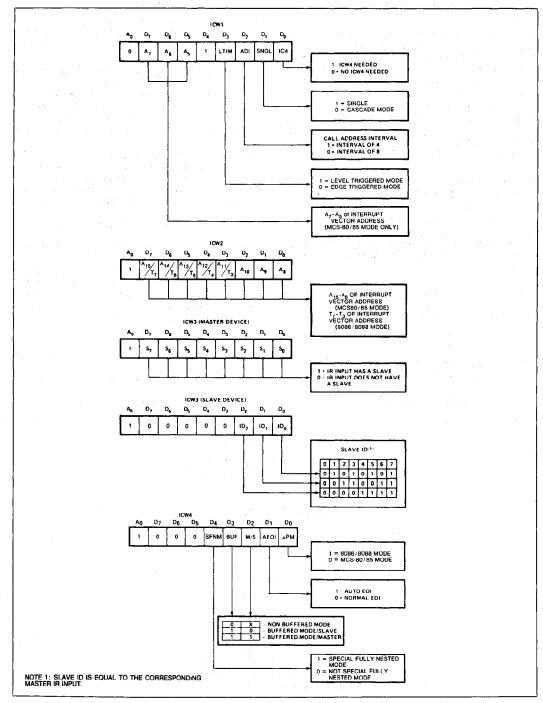

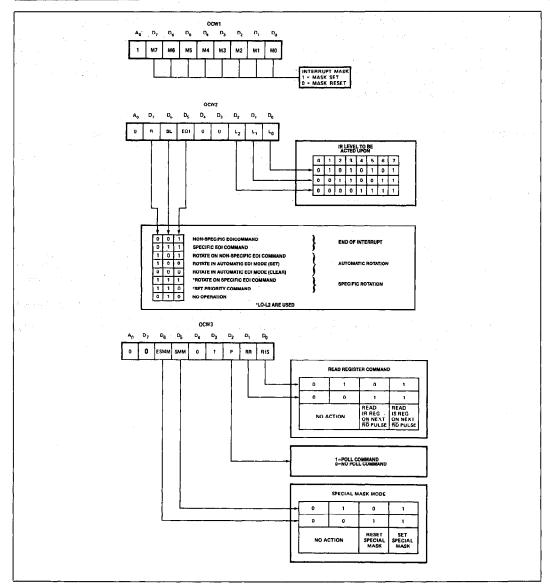

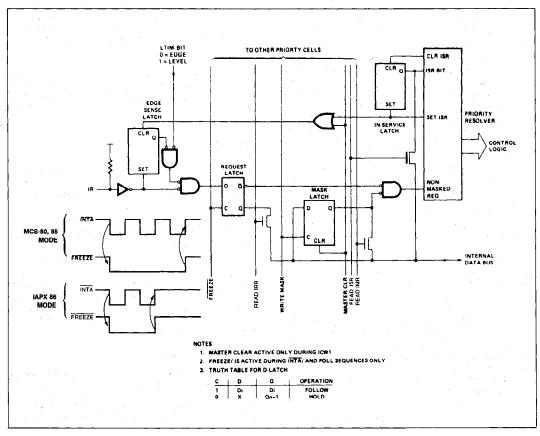

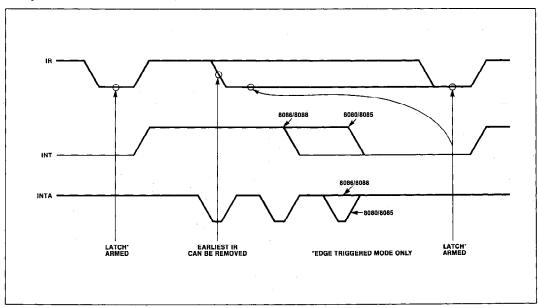

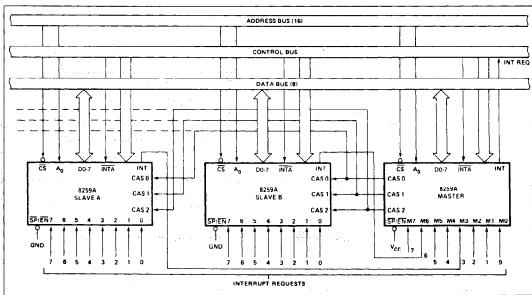

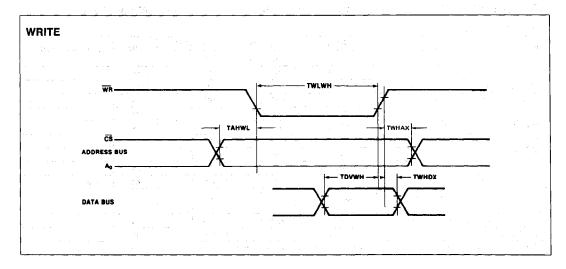

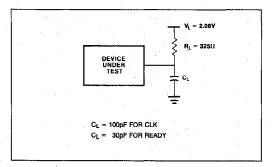

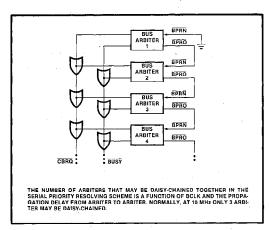

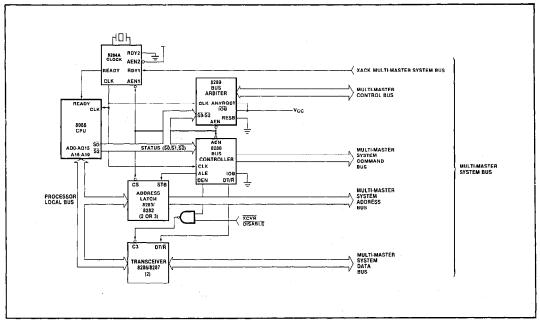

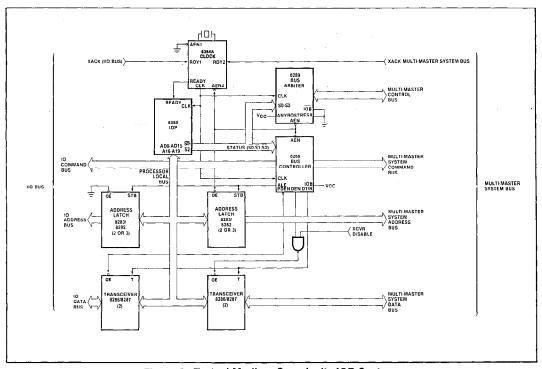

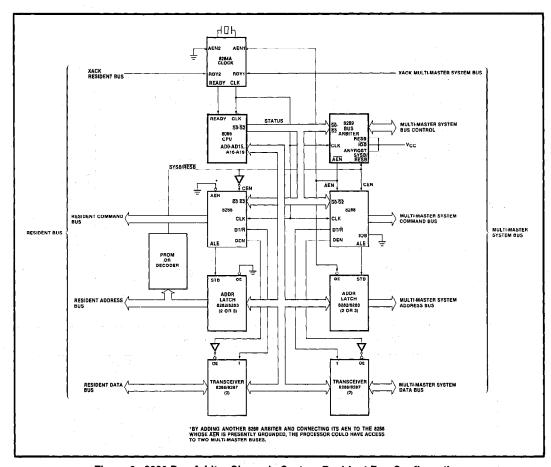

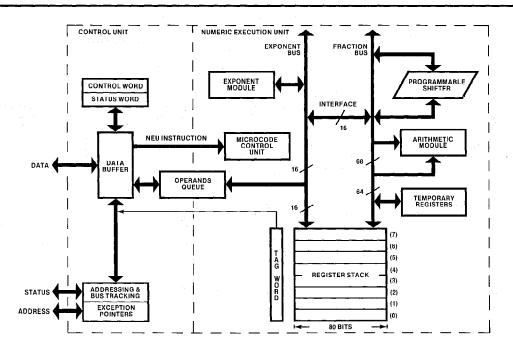

The reset signal to the 8086 can be generated by the 8284. The 8284 has a schmitt trigger input (RES) for generating reset from a low active external reset. The hysteresis specified in the 8284 data sheet implies that at least .25 volts will separate the 0 and 1 switching point of the 8284 reset input. Inputs without hysteresis will switch from low to high and high to low at approximately the same voltage threshold. The inputs are guaranteed to switch at specified low and high voltages (VIL and VIH) but the actual switching point is anywhere in-between. Since VIL min is specified at .8 volts, the hysteresis guarantees that the reset will be active until the input reaches at least 1.05 volts. A reset will not be recognized until the input drops at least .25 volts below the reset inputs VIH of 2.6 volts.